A/D转换器ADS8320的原理与应用

在便携式仪器设备中,往往要求其数据采集系统不仅具有速度快、精度高的特点,而且还要求其具有供电电压低、体积小以及功耗小等特性。ADS8320是 Burr-Brown公司生产的逐次逼近式串行16位微功耗CMOS型高速A/D转换器,它的线性度为±0.05%,工作电源在2.7V~5.25V范围内,采样频率最高可达100kHz;在2.7V供电和100kHz采样速率下,其功耗仅为1.8mW,而在10kHz低速采样时的功耗仅为0.3mW;在非转换状态时可处于关闭模式,此时功耗可低至100μW;ADS8320具有同步串行SPI/SSI接口,因而占用微处理器的端口较少;其差动输入信号范围为500mV~VCC(工作电源);采用8引脚MSOP小体积封装。以上特点使ADS8320非常适用于便携式电池供电系统中。

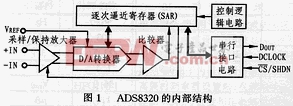

1 内部结构及引脚排列

ADS8320的内部结构如图1所示,它由采样/保持放大器、D/A转换器、比较器、移位寄存器、控制逻辑电路、串行接口电路等组成。其管脚排列如图2所示。各引脚的功能如下:

●VREF为外接参考电压输入端;

●+IN、-IN为外接差动模拟信号输入端;

●+Vcc、GND为供电电源接入端;

●CS/SHDN为片选/关断控制端;

●DCLOCK为时钟输入端;

●DOUT为A/D转换的数字结果串行输出端。

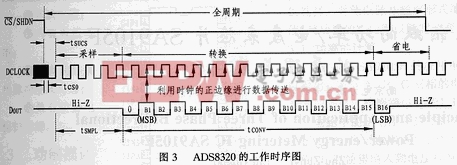

2 工作时序

ADS8320与微处理器或其它数字系统采用同步3线串行接口进行通信,其工作时序如图3所示。

当CS/SHDN 端从高电平变为低电平(下降沿)时,芯片的整个转换和数据传输过程被初始化,DCLOCK端的最初4.5~5个时钟脉冲用于对输入模拟信号的采样,此时 DOUT端处于高阻态;在随后的DCLOCK下降沿,DOUT端将输出一个可持续一个脉冲周期的低电平信号,以作为将要输出A/D转换结果的标志;紧接着在16个DCLOCK的控制下,从最高位(MSB)到最低位(LSB)依次由DOUT输出16位转换结果。

DCLOCK信号的下降沿可用来控制A/D转换结果在DOUT端的同步传输,大多数接收系统对DOUT端转换结果数字位流的采集在DCLOCK的上升沿进行。

当16 位转换结构传输结束后,若CS/SHDN端仍为低电平且DCLOCK端有控制脉冲,那么在DOUT端继续输出转换结果,但此时是由最低位(LSB)到最高位(MSB)依次输出,直到当最高位输出出现重复使DOUT端变成高阻态为止。即一次转换数据最多输出两次,一次从高位到低位,一次从低位到高位。一般情况下,当16位转换结果输出完毕后,置位或去掉DCLOCK脉冲,可使结果仅输出一次。

当CS/SHDN端接高电平(下降沿)时,ADS8320在关断模式下低功耗工作,只有当CS/SHDN端从高电平变为低电平时,芯片方可重新初始化而进行另一次A/D转换。

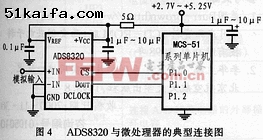

3 与单片机的典型接口设计

图4 以MCS-51系列单片机为例,给出了ADS8320与微处理的典型连接图。ADS8320采用单电源Vcc(2.7V~5.25V)供电,外接参考电源直接由供电电源来提供,此时模拟输入的最大范围为Vcc。串行接口的外部时钟DCLOCK及芯片的片选信号由单片机的P1.0口控制产生,转换结果由 P1.2读取。

在其它应用中,外接参考电源可在 500mV~Vcc之间选择,这同时决定了外接模拟电压的最大范围。但是过低的参考电压虽然可提高A/D转换的灵敏度且降低系统的抗干扰性能,同时需要连接更干净的低噪声电源,而且由于温漂、增益误差等原因也降低了A/D转换的线性度。如采用+5V参考电源,则内部噪声干扰的典型值为1.5LSB;而采用 +500mV参考电源时的内部噪声干扰典型值为15LSB。

外部接入时钟DCLOCK的频率可以在24kHz~2.4MHz之间变化,分别对应于1kHz和100kHz的A/D转换速率。该电路对外接时钟的占空比没有特点要求,而只需高、低电平的持续时间大于200ns即可。

外接模拟信号从+IN、-IN端差动输入以及CS/SHDN的下降沿使转换初始化后,它的前五个时钟脉冲为采样周期,这时差动输入信号被内部电容采样。而在转换过程中,+IN、-IN端与内部电路断开连接。为了保证转换的线性度,-IN端的电平即不能低于GND-100mV,也能高于GND+1V。+IN端的电平应保证在(GND-100mV)至(Vcc+100mV)之间。

A/D转换的数字结果将在DCLOCK端的控制下由DOUT端连续输出。如果DOUT端平时处于高阻态,则转换结束后首先出现低电平的标志位,随后输出从最高位到最低位的16位转换结果。

下面以MCS-51系列单片机为例,给出ADS8320与单片机接口的具体程序:

CS EQU P1.0

DOUT EQU P1.1

DCLOCK EQU P1.2

……

CONV:CLR CS

WAIT:ACALL DELAY

CLR DCLOCK

ACALL DELAY

SETB DCLOCK ;在DCLOCK端产生脉冲

MOV C,DOUT ;在DCLOCK上升沿采样

JC WAIT ;输出D OUT非零则等待

MOV R7, 16 ;读取16位转换结果

READ:CLR DCLOCK

ACALL DELAY

SETB DCLOCK :在DCLOCK端产生脉冲

MOV C,DOUT ;在DCLOCK上升沿

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 用ADS实现一个2.38GHz全集成化低噪声放大器设计(04-26)

- 基于ADS8364的数据采集系统设计(10-01)

- 发夹型滤波器的设计(10-23)

- 基于ADS1255的地震信息采集模块设计(12-01)