H.264/AVC中量化的Verilog实现

时间:01-08

来源:互联网

点击:

0 引 言

H.264作为新一代的视频压缩标准,是由ITU-T的视频编码专家组和ISO/IEC的MPEG(运动图像编码专家组)成立的联合视频小组共同开发的。它优异的压缩性能也将在数字电视广播、视频实时通信、网络视频流媒体传递以及多媒体通信等各个方面发挥重要的作用。

在核心技术上,H.264/AVC采用各种有效的技术,如统一的VLC符号编码、1/4像素精度的运动估计、多模式运动估计、基于4×4块的整数变换、分层编码语法等。由于采用了整数变换,计算不会出现浮点数,而且精度高等。这些措施使得H.264算法具有很高的编码效率。在量化方面,量化步长采用52个,下面将主要分析量化。在此,提出量化的Verilog实现,将变换后的数据作为输入,以量化后的码流作为输出,达到量化的目的。

1量化的功能介绍

取样后的脉冲信号在时间上是离散的,但在幅值和空间上仍是连续的,即其可能取的值有无限多个,这就需要对它采用四舍五入的方法,将其可能的幅值数由无限多个变为有限个值。这种将信号幅值由连续量变成离散量的过程称为量化。

在不降低视觉效果的前提下,量化过程可减少图像编码长度,减少视觉恢复中不必要的信息。H.264采用标量量化技术,将每个图像样点编码映射成较小的数值。一般标量量化器的原理为:

式中:y为输入样本点编码;QP为量化步长;FQ为y的量化值;round()取整函数(其输出与输入实数最近的整数)。

2量化的算法介绍

在H.264中,量化步长Qstep共有52个值。如表1所示。其中,QP是量化参数,是量化步长的序号。当QP取最小值0时,代表最精细的量化;当QP取最大值51时,代表最粗糙的量化。QP每增加6,Qstep增加1倍。应用时可以在这个较宽的量化步长范围根据实际需要灵活选择。对于色度编码,一般使用与亮度编码同样的量化步长。为了避免在较高量化步长时出现颜色量化人工效应,现在的H.264草案把色度的QP最大值大约限制在亮度QP最大值的80%范围内。最后的H.264草案规定,亮度QP的最大值是51;色度QP的最大值是39。

在H.264中,量化过程是对DCT的结果进行操作:

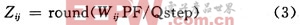

式中:Yij是矩阵Y中的转换系数;Zij是输出的量化系数;Qstep是量化步长。

H.264量化过程还要同时完成DCT变换中“Ef”乘法运算,它可以表述为:

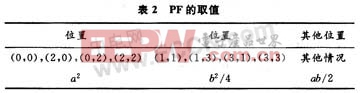

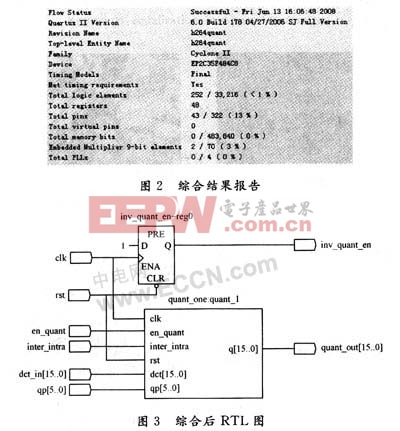

式中:Wij是矩阵W中的转换系数;PF是矩阵EF中的元素。根据样本点在图像中的位置(i,j)取值如表2所示。

利用量化步长随量化参数每增加6而增加1倍的性质,可以进一步简化计算,即:

式中:floor()为取整函数(其输出不大于输入实数的最大整数)。式(3)可以写为:

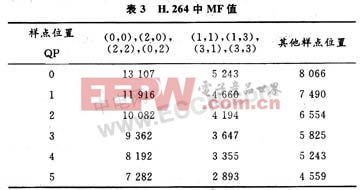

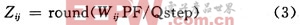

这样,MF可以取整数。表3给出对应QP值为0~5的MF值。对于QP值大于5的情况,只是qbits值随QP值每增加6而增加1,而对应的MF值不变。这样,量化过程为整数运算,可以避免使用除法,确保用16位算法来处理数据,在没有PSNR性能恶化的情况下,实现最小的运算复杂度如表3所示。

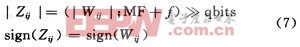

具体量化过程的运算为:

式中:“》”为右移运算,右移1次完成整数除以2;sign()为符号函数;f为偏移量。f的作用是改善恢复图像的视觉效果,如对帧内预测图像块f取2qbits/3;对帧间预测图像块厂取2qbits/6。

3具体实现

在该文中,用Verilog语言实现H.264的量化;运用Modelsim进行仿真;用QuartusⅡ进行综合。

根据Verilog编程,Modelsim仿真如图1所示。

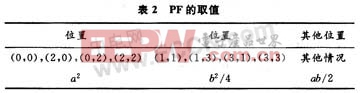

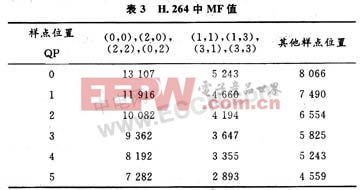

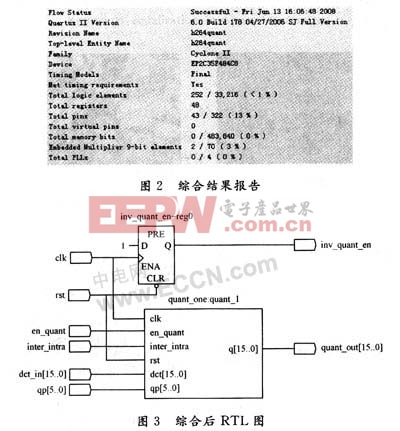

输入的矩阵是[140,-1,-6,7,-19,-39,7,-92,22,17,8,31,-27,-32,-59,-21],最后量化的结果为[17,0,-1,0,-1,-2,0,-5,3,1,1,2,-2,-1,-5,-1]。由此可知,这与Iain E.G.Richardson给出的结果相符合。所用的开发板是红色飓风第三代开发板,FPGA芯片是Altra EP2C35F484C8。从综合后的报告可以看出,消耗的资源不到1%,如图2所示。综合后的RTL图如图3所示。

4结 语

介绍了H.264的量化算法,并用Modelsim进行了仿真,结果与理论完全一致。分析了在FPGA开发板上的资源的消耗。由此可知,完全可以用FPGA实现H.264的量化。

H.264作为新一代的视频压缩标准,是由ITU-T的视频编码专家组和ISO/IEC的MPEG(运动图像编码专家组)成立的联合视频小组共同开发的。它优异的压缩性能也将在数字电视广播、视频实时通信、网络视频流媒体传递以及多媒体通信等各个方面发挥重要的作用。

在核心技术上,H.264/AVC采用各种有效的技术,如统一的VLC符号编码、1/4像素精度的运动估计、多模式运动估计、基于4×4块的整数变换、分层编码语法等。由于采用了整数变换,计算不会出现浮点数,而且精度高等。这些措施使得H.264算法具有很高的编码效率。在量化方面,量化步长采用52个,下面将主要分析量化。在此,提出量化的Verilog实现,将变换后的数据作为输入,以量化后的码流作为输出,达到量化的目的。

1量化的功能介绍

取样后的脉冲信号在时间上是离散的,但在幅值和空间上仍是连续的,即其可能取的值有无限多个,这就需要对它采用四舍五入的方法,将其可能的幅值数由无限多个变为有限个值。这种将信号幅值由连续量变成离散量的过程称为量化。

在不降低视觉效果的前提下,量化过程可减少图像编码长度,减少视觉恢复中不必要的信息。H.264采用标量量化技术,将每个图像样点编码映射成较小的数值。一般标量量化器的原理为:

式中:y为输入样本点编码;QP为量化步长;FQ为y的量化值;round()取整函数(其输出与输入实数最近的整数)。

2量化的算法介绍

在H.264中,量化步长Qstep共有52个值。如表1所示。其中,QP是量化参数,是量化步长的序号。当QP取最小值0时,代表最精细的量化;当QP取最大值51时,代表最粗糙的量化。QP每增加6,Qstep增加1倍。应用时可以在这个较宽的量化步长范围根据实际需要灵活选择。对于色度编码,一般使用与亮度编码同样的量化步长。为了避免在较高量化步长时出现颜色量化人工效应,现在的H.264草案把色度的QP最大值大约限制在亮度QP最大值的80%范围内。最后的H.264草案规定,亮度QP的最大值是51;色度QP的最大值是39。

在H.264中,量化过程是对DCT的结果进行操作:

式中:Yij是矩阵Y中的转换系数;Zij是输出的量化系数;Qstep是量化步长。

H.264量化过程还要同时完成DCT变换中“Ef”乘法运算,它可以表述为:

式中:Wij是矩阵W中的转换系数;PF是矩阵EF中的元素。根据样本点在图像中的位置(i,j)取值如表2所示。

利用量化步长随量化参数每增加6而增加1倍的性质,可以进一步简化计算,即:

式中:floor()为取整函数(其输出不大于输入实数的最大整数)。式(3)可以写为:

这样,MF可以取整数。表3给出对应QP值为0~5的MF值。对于QP值大于5的情况,只是qbits值随QP值每增加6而增加1,而对应的MF值不变。这样,量化过程为整数运算,可以避免使用除法,确保用16位算法来处理数据,在没有PSNR性能恶化的情况下,实现最小的运算复杂度如表3所示。

具体量化过程的运算为:

式中:“》”为右移运算,右移1次完成整数除以2;sign()为符号函数;f为偏移量。f的作用是改善恢复图像的视觉效果,如对帧内预测图像块f取2qbits/3;对帧间预测图像块厂取2qbits/6。

3具体实现

在该文中,用Verilog语言实现H.264的量化;运用Modelsim进行仿真;用QuartusⅡ进行综合。

根据Verilog编程,Modelsim仿真如图1所示。

输入的矩阵是[140,-1,-6,7,-19,-39,7,-92,22,17,8,31,-27,-32,-59,-21],最后量化的结果为[17,0,-1,0,-1,-2,0,-5,3,1,1,2,-2,-1,-5,-1]。由此可知,这与Iain E.G.Richardson给出的结果相符合。所用的开发板是红色飓风第三代开发板,FPGA芯片是Altra EP2C35F484C8。从综合后的报告可以看出,消耗的资源不到1%,如图2所示。综合后的RTL图如图3所示。

4结 语

介绍了H.264的量化算法,并用Modelsim进行了仿真,结果与理论完全一致。分析了在FPGA开发板上的资源的消耗。由此可知,完全可以用FPGA实现H.264的量化。

- PCM串行数据流同步时钟提取设计(02-25)

- 一种数模混合SoC设计协同仿真的验证方法(04-09)

- 基于FPGA的∑-△D/A转换器的设计与实现(04-23)

- 基于ISP芯片的可编程数字移相器设计(06-23)

- 一种锁定相位编程可调全数字锁相环设计(06-24)

- 基于Virtuoso平台的单片射频收发系统电路仿真与版图设计(07-18)