通过改善视频解码器和编解码器接口降低DVR系统成本

1)采用高分辨率模数转换和先进亮度/色度分离技术的多通道视频解码器,可将质量及信噪比(SNR)最大化;

2)支持 H.264 及其他先进压缩技术的视频编解码器SoC,可最大限度降低比特率,实现HDD 存储容量的最大化。

当然,还有许多其他的技术因素,如不断进步的处理器、网络和存储器等,都在不断改善着监控DVR 的品质。尽管如此,这些技术也得益于其它技术市场的推动。下面,我们将介绍主要面向视频监控应用进行开发的多通道视频解码器和编解码器。

视频监控DVR的架构大有不同,这主要取决于终端用户的要求。通常,监控DVR接受来自多个模拟相机的输入,并将视频数字化;然后,将原始数字视频传送到编解码器进行压缩(在一些基于 PC的架构中,压缩用软件执行,但是大多数 DVR采用硬件编解码器)。

大多数DVR还提供“预览”或“实时显示”模式,允许在相机上实时观看现场事件,是“数字视频录像机”的“录像机”部分,意味着该器件需要压缩和存储视频。反过来,这意味着DVR系统必须能够将从视频解码器中获得的未压缩视频传送到编解码器进行压缩。这看起来非常简单,但实际上,当视频解码器的输出不兼容,或输出不是编解码器输入的最理想模式时,就会产生严峻挑战。ITU-R BT.656是一个未压缩数字视频的正式标准,但为了节省引脚和印制线,许多编解码器都要求具有多个视频流交错在一起的超频 BT.656。尽管提出了详细的分辨率和计时要求,但是交错基本方法并非标准。

因为 I/O 引脚数的限制,许多编解码器都要求字节交错数据,这样2或4个数字视频流就可以与来自每个视频流的交替数据字节进行多路传输。有些编解码器可以接受线交错数据,在这些器件中,所有视频流组成的一个完整视频队列在下一次视频流队列之前被送出,如此反复。为了进一步挑战监控 DVR 系统设计人员,大多数编解码器都要求帧交错视频数据,而来自各个源的整个帧都是按顺序输入的,以实现其最高工作效率。即使在字节或线交错数据发送到编解码器的情况下,无论如何也必须将数据解复用成帧,用于每个源。在输入引脚上直接接收帧交错视频数据,可以降低这种难度,对于编解码器来说是处理器密集型应用。

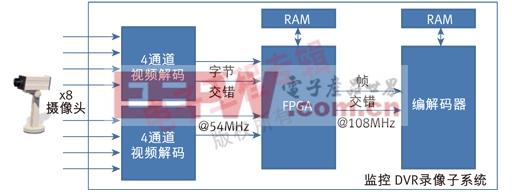

因为编解码器通常是监控 DVR 中所使用的最昂贵、最复杂的硅器件(不包括用于基于PC 的DVR的微处理器),大多数系统设计人员都希望编解码器以最高效率运行,所以许多设计人员采用外部逻辑来生成帧交错数据以发送到编解码器。图1显示了采用FPGA的监控 DVR录像子系统,执行从视频解码器54MHz字节交错数据到编解码器108MHz帧交错数据的转换。

图 1:使用FPGA进行未压缩视频格式转换的子系统

因为大多数多通道视频解码器不支持帧交错数据格式,而这种格式恰恰对于编解码器是最佳的,或是在某些情况下是必须的,因此需要用FPGA来转换数据。这是个令人满意的解决方案,但是FPGA 增加了设计的成本和复杂性。如果视频解码器可提供帧交错数据,FPGA就可以完全从子系统中移除。

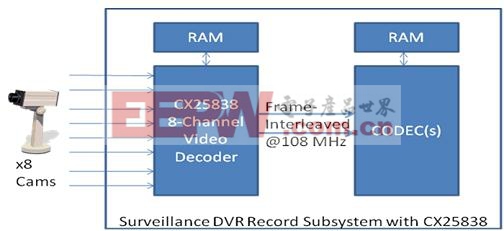

为了应对这个挑战并降低集成成本,科胜迅系统公司新近推出8通道视频解码器CX25838和CX25858,可提供帧交错输出并与监控DVR中普遍使用的编解码器兼容。图2显示了当带有帧交错输出的CX25838 发送到图1所示子系统时,子系统结构图是如何改变的。

图 2:带帧交错输出的基于 8 通道视频解码器的子系统

8 通道架构和帧交错输出可帮助录像子系统实现可能最高水平的集成,由于不再需要FPGA和 4通道解码器,所以可以将元件数量减少到2个。这不仅节省了成本,还节省了宝贵的板上空间。那么,该产品的灵活性怎样呢?虽然FPGA和可编程逻辑为定制化提供了最广泛的选择,但是CX25838也非常灵活。为了处理各种系统要求,CX25838 能够输出各种分辨率和帧速率。CX25838上有4条专用8位视频I/O总线。图3说明了CX25838 的一条8位视频输出总线上的帧交错数据格式的例子。

CX25838为监控DVR设计人员提供机会,通过提供帧交错数据实现编解码器效率最大化,而不采用昂贵的FPGA或可编程逻辑。它还通过提供各种分辨率和帧速率,在一系列产品中共享系统架构,提供规模优势的能力。例如,低成本DVR可采用一个编解码器以全帧速率压缩16个CIF分辨率通道,这可通过一条8位总线实现。其他解决方案可能需要每个编解码器以全帧速率压缩

- 超级电容器储能的直流DVR装置的研发(04-01)

- 基于超级电容器储能的直流DVR装置的研发(08-17)

- 数字录像机(DVR)和数字视频服务器(SVR)(07-17)

- 视频解码器SAA7111在图像采集中的应用(06-21)

- 应用于汽车电子的音频插孔开关(06-27)

- MAX98090超低功耗音频编解码器(10-14)