TLV2544/2548多通道12位串行A/D转换器

*这些位仅在10和11转换模式中有效

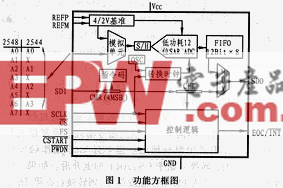

TLV2544/2548两芯片的内部功能结构相同,不同之处就是前者的模拟输入通道为4路,而后者为8路。下面以TLV2544为例为介绍。 2 工作原理 TLV2544有4路模拟输入和3个内部测试输入端,它们可由模拟多路转换器根据输入的命令来选择。输入多路转换器采用先开后合型,因为这可减少由通道切换引起的输入噪声。 TLV2544 的工作周期的开始模式有两种:一种是当不使用FS时(在CS的下降沿FS=1),CS的下降沿即为周期的开始。这时的输入数据在SCLK的上升沿移入,输出数据下降沿改变。这种模式虽然也可用于DSP,但一般常用于SPI微控制器。另一种是当使用FS时(FS是来自DSP的有效信号),FS的下降沿即为周期的开始,这时的输入数据在SCLK的下降沿移入,输出数据在其上升沿改变,这种模式一般用于TMS320系列的DSP。 TLV2544 具有一个4位命令集(存于命令寄存器CMR中)和一个12位配置数据域。大多数命令只需要前4个MSB,即不需要低12位数据。值得注意的是,器件在上电初始化时首先需要将将始化命令A000h写入CFR配置寄存器,然后对器件进行编程,其编程方法是在初始化命令A000h的低12位000h写入编程数据以规定器件的工作方式。编程定义如表2所列,编程信息被保留在H/W或S/W的断电状态。当器件被编程时,由微处理发送一个16位串行数据写入CFR,如果在输入了前8位后SCLK中断,那么余下的8位则在SCLK被恢复后再输入。一个读CFR命令可读出CFR的状态,以校验写入控制命令是否正确,其他控制命令可参见表3。

如果前高4位输入数据被译码为转换命令之一,那么采样周期开始。一般有两种采样方式:正常采样和扩展采样。正常采样实际上是采用软件启动A/D变换方式,当 A/D转换器正常采样时,采样周期是可编程的,它可以是12SCLKs(短周期采样)或24SCLKs(长周期采样)。当SCLK高于10MHz或输入源

D2

EOC/INT引脚功能选择,0;引脚用作INT;1:引脚用作EOC

D(1,0)

FIFO触发器电平(扫描序列长度)

00:全部(FIFO level 7填满后产生INT)

01:3/4(FIFO level 5填满后产生INT)

10:1/2(FIFO level 3填满后产生INT)

11:1/4(FIFO level 1填满后产生INT)

表3 TLV2544/TLV2548命令集

SDID(15~12)BINary HEX

TLV2548指命

TLV2544指命

0000b

0000h

选择模拟通道0

选择模拟通道0

0001b

1000h

选择模拟通道1

N/A

0010b

2000h

选择模拟通道2

选择模拟通道1

0011b

3000h

选择模拟通道3

N/A

0100b

4000h

选择模拟通道4

选择模拟通道2

0101b

5000h

选择模拟通道5

N/A

0110b

6000h

选择模拟通道6

选择模拟通道3

0111b

7000h

选择模拟通道7

N/A

1000b

8000h

选择模拟通道8

SW电源跌落(模拟+参考)

1001b

9000h

读CFR寄存器数据到SDO D(11~0)

1010b

A000h plus data

将低12位数据写CFR

1011B

B000h

测试选择,电压为(REFP+REFR)/2

1100b

C000h

测试选择,电压为REFM

1101b

D000h

测试选择,电压为REFP

1110b

E000h

FIFO读,将FIFO内容送SDO D(15~4),D(3~0)=0000

1111b

F000h plus data

保留

- DPA-Switch为应对PoE受电设备设计挑战提供有效解决方案(11-06)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 用LatticeXP FPGA 桥接吉比特媒体独立接口(01-18)

- 单片机与串行AD转换器TLC0834的接口设计(01-22)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)