应用于音频放大器的多位Σ-Δ调制器的设计

一般来说,高阶Σ-Δ调制器比低阶Σ-Δ调制器具有更好的性能。但大于二阶的不能用线性模型描述,因为比较器的平均增益减小,使系统的稳定性下降。多级噪声模型是解决稳定性较好的方案。该技术采用了多个级联、稳定的一阶回路,每阶回路对上一级的积分器输出与数模转换器(DAC)输出之差(量化噪声)进行量化,最后差分求和输出,它能够使量化噪声得到很好的抑制。多位结构的Σ-Δ调制器则可提高转换速率和精度。对于一个给定的过采样比和滤波器的阶数,这种结构可以提供更大的动态范围。多位调制器每增加1位,信噪比就能增加6dB,而且它还可以减少带外的噪声水平,降低对后级模拟滤波器的要求。但多位调制器的一个主要缺点是:由于在多位DAC中的元素不匹配而造成的积分非线性化问题,使每级的非线性化误差得不到消除而逐渐累加而造成输出结果恶化。本文提出了一种方法:在传统的MASH结构基础上,每级之间加一条反馈回路[3]。该方法能有效地消除多位DAC非线性化而带来的误差。

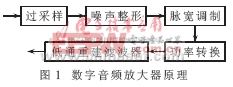

1 调制器原理

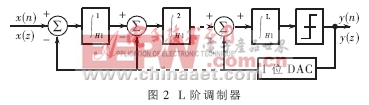

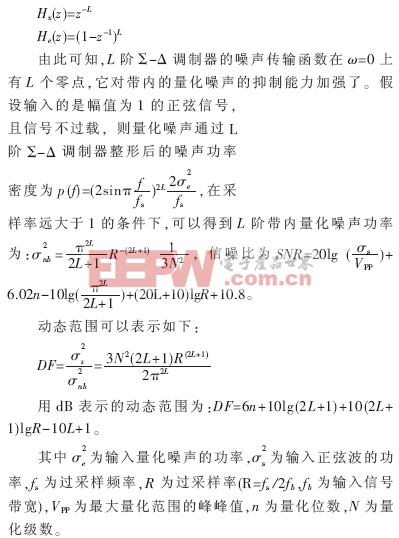

L阶Σ-Δ调制器如图2所示。Σ-Δ调制器的阶数就是调制器前向通道积分器的个数。从图中可以看出,L阶Σ-Δ调制器的前向通道包括L个积分器和嵌于反馈回路的量化器,每个积分器的输入均为前一个积分器的输出与1位DAC的输出之差。反馈回路的作用使得第一级积分器的净输入趋于零,即DAC的输出与调制器的输入信号X(n)基本相等,亦即X(n)≈Y(n)。

由于量化器为非线性元件,为了分析它所引入的量化误差,需将量化器近似等效成一个相加性的白噪声源e(n),因此根据线性化系统叠加原理,得到调制器对信号和噪声的传输函数如下:

从以上公式可以看出,增加阶数、位数和过采样率都可以让调制器的信噪比和动态范围有不同程度的提高。但随着它们的提高,也会带来负面影响。在过采样率一定的情况下,增加位数能够弥补阶数变高而引起的动态范围减小的问题,信噪比也会提高,但它引入的非线性误差却会使结果恶化。在减小多位系统中的DAC非线性化问题方面,人们提出了很多解决办法,包括引入新的结构、校准技术、动态元素匹配技术(DEM)、双端量化结构等[4]。在上述的方法中,动态元素匹配技术在解决多位系统中的非线性化问题中是应用最广的。它通过计算出不匹配单元造成的误差,从而得到一个修正算法,通常用得较多的算法有元素随机化和元素旋转等。但DEM的缺陷是强烈依靠它所使用的算法。例如DEM广泛使用的DWA数据权重平均算法虽然能够对第一阶的噪声进行整形,但是它也引入了信号依赖误差而降低了动态范围,虽然改进的双向DWA算法能够降低信号依赖误差,但是使带内的噪声同时也增加了。因此,DEM大体上只是用在一阶噪声整形上[5]。为此本文提出了一种没有采用DEM的4阶级联调制器的新方案,它在解决非线性化的问题上取得了较好的

- 广泛应用于传感器的电流输入型前置放大器电路及工作原理(10-16)

- 一种应用于D类音频放大器的CMOS振荡器的设计(04-23)

- 广泛应用于传感器的电流输入型前置放大器电路及工(02-18)

- PAC应用于某动力系统训练模拟器中(07-20)

- 低EMI、D类音频放大器及其应用(06-21)

- 高性能音频放大器的设计准则与技巧(07-02)