高速双通道采样芯片AT84AD001B及其应用

时间:03-29

来源:互联网

点击:

在雷达、通信、医疗等领域的系统设计中都需要对信号进行高速处理,因而高速AD转换芯片的选择就显得至关重要。目前生产高速AD转换芯片的厂商主要有ATMEL、MAXIM、Rock-well、ADI、TI等。AT84AD001B就是一款由AT-MEL出品的AD采样芯片,可支持单/双通道、单/双路时钟控制、及MUX1:1、MUX1:2等多种工作模式,采样速率最高可达1GSPS(交错模式下最高可达2GSPS),能够广泛应用于各种高速信号采集系统。文中主要就AT84AD001B的工作原理、工作方式及具体应用设计作以介绍。

1 AT84AD001B的特点

AT84AD001B是一种Flash型ADC,其采样速率最高可达1GSPS,在交错模式下最高可达2GSPS。该芯片的主要特点有:支持单路或MUX1:2模式输出。输入信号为峰峰值小于或等于500 mV的差分信号:输出数字信号为LVDS电平方式,且可以通过三线串口配置为二进制式或格雷码式:输人时钟可以为单端或差分PECL/LVDS方式,串联匹配电阻为50欧姆;需要提供的电源有3.3 V模拟电源,3.3 V数字电源,及2.25V的输出驱动电源:封装形式为LQFP144。满功率输入带宽为1.5 GHz(-3 dB);有很高的信噪比,在1GSPS时误码率仅为10-13;支持三线串口,可对工作方式进行配置。相比于其他ADC芯片,AT84AD001B的功耗更低。每一通道的功耗为0.7W,在休眠模式下功耗可低至120 mW。

2 Flash型ADC的工作原理

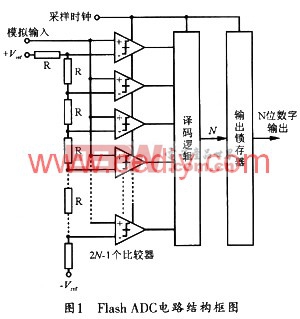

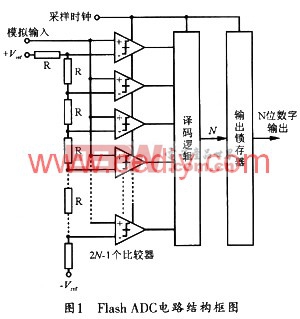

AT84AD001B采用Flash型ADC结构。其内部电路结构框图如图1所示。

由于Flash ADC只需一次转换即可得出数据,且比较器是同时工作的,因此模数转换的速度取决于一级比较器的延迟时间以及编码器和辅助电路中逻辑门的延迟时间,其速度极快。

Flash ADC由分压电阻网络、电压比较器阵列、译码逻辑单元和输出锁存器组成。这一种Flash ADC采用大量的比较器和电阻,对于N位分辨率的Flash ADC,其转换器包含2N个电阻和2N-1个电压比较器。参考电压VREF首先被分为2N阶,即VREF/2N,2VREF/2N,3VREF/2N,……(2N-1)VREF/2N,接着将这2N阶参考电压分别加到这些电压比较器的参考端,并将模拟输入电压加到所有电压比较器的输入端。然后由比较器对这两端的电压进行比较。将输入端电压高于参考电压的比较器输出为1,否则输出为0。这2N-1个比较器的输出连同0电势输出再经过译码逻辑便可获得N位二进制数,最后经输出锁存器保存在输出端。Flash ADC的采样时序控制由采样时钟来完成。

3 AT84AD001B的内部结构

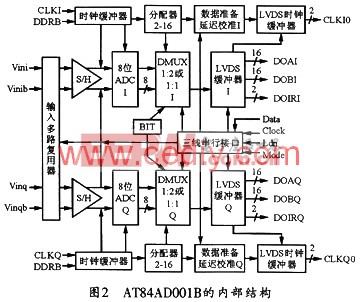

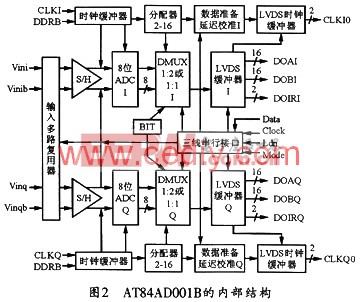

AT84AD001B中集成了两路(I和Q)独立的ADC转换器,且具有8bit转换精度,每个通道具有1GSPS的采样率,在交错模式下两路ADC并行采样可以达到2 GSPS的采样率。AT84AD001B内部集成了1:1和1:2的数据多路分离器(DMUX)和LVDS输出缓冲器,可以降低输出数据率,也可以方便地与多种类型的高速FPGA直接相连,以实现高速率的数据缓存及处理。AT84AD001B内部还集成了时钟选择器,可以根据具体需要方便的选择单路时钟或双路时钟来控制采样。AT84AD001B的内部结构如图2所示。

4 AT84AD001B的三线串口

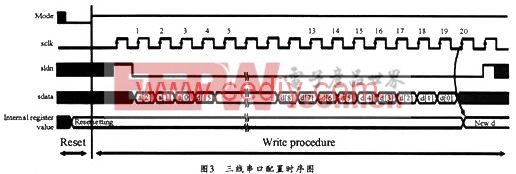

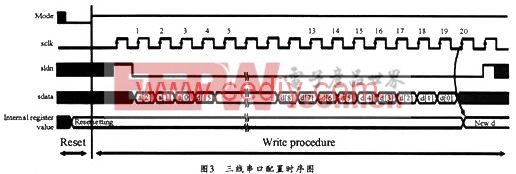

AT84AD001B高速模数转换器芯片的MODE、CLK、LDN及DATA 4个引脚可用于三线串口的配置。其中MODE引脚用于配置选择是否启用三线串口,MODE为高时启用三线串口,为低时屏蔽,参数为缺省状态。CLK是三线串口的配置时钟输入引脚。LDN为配置通过三线串口配置寄存器的开始和结束信号输入引脚。DATA为三线串口的寄存器配置数据输入引脚。CLK引脚允许输入的最大时钟频率是50 MHz。三线串口配置时序见图3所示。

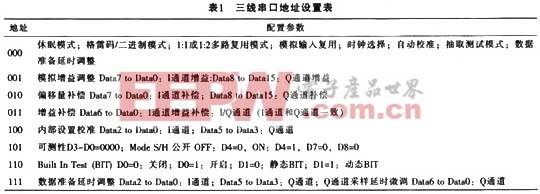

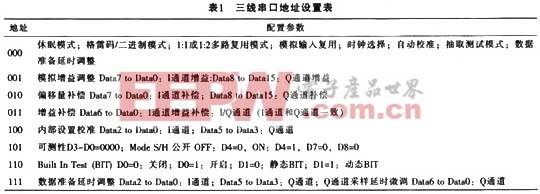

在对AT84AD001B高速模数转换器芯片的应用电路进行设计时,可以通过微处理器对三线串行接口进行配置。通常在高速信号处理系统中通过后端做信号处理的高速FPGA对三线串口进行配置,而无需添加专用芯片,因此可以节省空间,利于PCB设计。系统启动或复位后,当MODE脚为高电平,LDN脚为低电平时,DATA脚将会在每一个CLK的上升沿输入1 bit数据。由于每个三线串口寄存器需输入的配置数据包括3 bit的寄存器地址和送入该寄存器的16 bit数据,因此该设计总共需配置8个寄存器,表1是各寄存器的配置参数。

5 AT84AD001B的工作模式

AT84AD001B的工作方式按输入的模拟信号来分,具有以下三种模式:

(1)I通道与Q通道有相互独立的两路输入;

(2)I通道与Q通道均使用I通道的模拟输入;

(3)I通道与Q通道均使用Q通道的模拟输入。

AT84AD001B的工作方式按时钟输入也可以分为三种:

(1)I通道和Q通道有各自独立的时钟,分别在上升沿时采样;

(2)两个通道都使用I通道时钟,在I通道时钟的上升沿采样;

(3)两个通道都使用I通道的时钟,ADC内部产生一个同频反相的时钟作为Q通道工作时钟。在第3种模式下,当两通道输入同一模拟信号时,就可以实现交替式并行采样。ADC的采样速率为输人工作时钟的2倍。

AT84AD0001B的工作方式有多种选择,用户可以根据自身系统的需要和特点来选择最合适的工作模式。

6高速采样设计

采用AT84AD001B和高速FPGA来实现采样系统的设计应遵循两个原则:一是要有足够的专用LVDS差分逻辑接收通道:二是用作AD输出差分数据接收的专用LVDS差分逻辑接收通道的最高数据传输速率要大于AD的数据输出速率。

本设计中的AT84AD001B与高速FPGA的接口设计如图4所示。

图中FPGA用于产生AD的时钟和三线串口配置信号,由于AD的采样输出信号速率很高,设计中需要通过串并转换或数据抽取使数据速率降低之后,才能对信号进行处理,而不宜直接做信号处理。

7结束语

由于AT84AD001B的工作方式灵活多样,所以基于它的高速采样系统的设计也很灵活,因此可以根据目标系统的需求或指标来满足系统的设计要求。而且,AT84AD001B的这种灵活性也方便了它在其他领域中的推广。

1 AT84AD001B的特点

AT84AD001B是一种Flash型ADC,其采样速率最高可达1GSPS,在交错模式下最高可达2GSPS。该芯片的主要特点有:支持单路或MUX1:2模式输出。输入信号为峰峰值小于或等于500 mV的差分信号:输出数字信号为LVDS电平方式,且可以通过三线串口配置为二进制式或格雷码式:输人时钟可以为单端或差分PECL/LVDS方式,串联匹配电阻为50欧姆;需要提供的电源有3.3 V模拟电源,3.3 V数字电源,及2.25V的输出驱动电源:封装形式为LQFP144。满功率输入带宽为1.5 GHz(-3 dB);有很高的信噪比,在1GSPS时误码率仅为10-13;支持三线串口,可对工作方式进行配置。相比于其他ADC芯片,AT84AD001B的功耗更低。每一通道的功耗为0.7W,在休眠模式下功耗可低至120 mW。

2 Flash型ADC的工作原理

AT84AD001B采用Flash型ADC结构。其内部电路结构框图如图1所示。

由于Flash ADC只需一次转换即可得出数据,且比较器是同时工作的,因此模数转换的速度取决于一级比较器的延迟时间以及编码器和辅助电路中逻辑门的延迟时间,其速度极快。

Flash ADC由分压电阻网络、电压比较器阵列、译码逻辑单元和输出锁存器组成。这一种Flash ADC采用大量的比较器和电阻,对于N位分辨率的Flash ADC,其转换器包含2N个电阻和2N-1个电压比较器。参考电压VREF首先被分为2N阶,即VREF/2N,2VREF/2N,3VREF/2N,……(2N-1)VREF/2N,接着将这2N阶参考电压分别加到这些电压比较器的参考端,并将模拟输入电压加到所有电压比较器的输入端。然后由比较器对这两端的电压进行比较。将输入端电压高于参考电压的比较器输出为1,否则输出为0。这2N-1个比较器的输出连同0电势输出再经过译码逻辑便可获得N位二进制数,最后经输出锁存器保存在输出端。Flash ADC的采样时序控制由采样时钟来完成。

3 AT84AD001B的内部结构

AT84AD001B中集成了两路(I和Q)独立的ADC转换器,且具有8bit转换精度,每个通道具有1GSPS的采样率,在交错模式下两路ADC并行采样可以达到2 GSPS的采样率。AT84AD001B内部集成了1:1和1:2的数据多路分离器(DMUX)和LVDS输出缓冲器,可以降低输出数据率,也可以方便地与多种类型的高速FPGA直接相连,以实现高速率的数据缓存及处理。AT84AD001B内部还集成了时钟选择器,可以根据具体需要方便的选择单路时钟或双路时钟来控制采样。AT84AD001B的内部结构如图2所示。

4 AT84AD001B的三线串口

AT84AD001B高速模数转换器芯片的MODE、CLK、LDN及DATA 4个引脚可用于三线串口的配置。其中MODE引脚用于配置选择是否启用三线串口,MODE为高时启用三线串口,为低时屏蔽,参数为缺省状态。CLK是三线串口的配置时钟输入引脚。LDN为配置通过三线串口配置寄存器的开始和结束信号输入引脚。DATA为三线串口的寄存器配置数据输入引脚。CLK引脚允许输入的最大时钟频率是50 MHz。三线串口配置时序见图3所示。

在对AT84AD001B高速模数转换器芯片的应用电路进行设计时,可以通过微处理器对三线串行接口进行配置。通常在高速信号处理系统中通过后端做信号处理的高速FPGA对三线串口进行配置,而无需添加专用芯片,因此可以节省空间,利于PCB设计。系统启动或复位后,当MODE脚为高电平,LDN脚为低电平时,DATA脚将会在每一个CLK的上升沿输入1 bit数据。由于每个三线串口寄存器需输入的配置数据包括3 bit的寄存器地址和送入该寄存器的16 bit数据,因此该设计总共需配置8个寄存器,表1是各寄存器的配置参数。

5 AT84AD001B的工作模式

AT84AD001B的工作方式按输入的模拟信号来分,具有以下三种模式:

(1)I通道与Q通道有相互独立的两路输入;

(2)I通道与Q通道均使用I通道的模拟输入;

(3)I通道与Q通道均使用Q通道的模拟输入。

AT84AD001B的工作方式按时钟输入也可以分为三种:

(1)I通道和Q通道有各自独立的时钟,分别在上升沿时采样;

(2)两个通道都使用I通道时钟,在I通道时钟的上升沿采样;

(3)两个通道都使用I通道的时钟,ADC内部产生一个同频反相的时钟作为Q通道工作时钟。在第3种模式下,当两通道输入同一模拟信号时,就可以实现交替式并行采样。ADC的采样速率为输人工作时钟的2倍。

AT84AD0001B的工作方式有多种选择,用户可以根据自身系统的需要和特点来选择最合适的工作模式。

6高速采样设计

采用AT84AD001B和高速FPGA来实现采样系统的设计应遵循两个原则:一是要有足够的专用LVDS差分逻辑接收通道:二是用作AD输出差分数据接收的专用LVDS差分逻辑接收通道的最高数据传输速率要大于AD的数据输出速率。

本设计中的AT84AD001B与高速FPGA的接口设计如图4所示。

图中FPGA用于产生AD的时钟和三线串口配置信号,由于AD的采样输出信号速率很高,设计中需要通过串并转换或数据抽取使数据速率降低之后,才能对信号进行处理,而不宜直接做信号处理。

7结束语

由于AT84AD001B的工作方式灵活多样,所以基于它的高速采样系统的设计也很灵活,因此可以根据目标系统的需求或指标来满足系统的设计要求。而且,AT84AD001B的这种灵活性也方便了它在其他领域中的推广。

- 适合LED街灯应用的高能效28 V、3.3 A LED驱动器设计(07-30)

- 解析LED区域照明的驱动架构以及典型设计方案(01-23)

- 基于USB单片机的模拟电梯设计与实现(10-16)

- 8位1.0GSPS ADC芯片MXT2001原理与应用(11-07)

- MAX24001突发模式激光收发器(10-15)

- 凌力尔特推出降压型微型模块 (μModule) 稳压器 LTM8001(08-28)