平衡功率放大器的设计与实现

1 平衡放大器工作原理

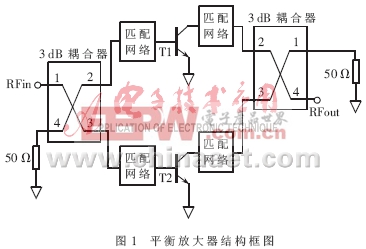

平衡放大电路采用2个3 dB混合耦合器和2个射频放大芯片构成对称电路,通过隔离入射信号和反射信号,从而实现频带范围内功率增益的平坦和降低输入、输出端口的驻波比,电路结构框图如图1所示[3]。

因为平衡放大电路中包含了3 dB耦合器,所以有必要先分析一下3 dB耦合器的传输特性。参考图1来描述3 dB耦合器的传输特性:(1)如果射频信号从1端口输入其他端口连接匹配负载,则1端口入射的射频信号的功率被平均分配到2端口和3端口输出并且输出信号的相位在2端口相对于3端口超前П/2,在4端口由于信号抵消而没有功率输出;(2)如果2端口和3端口输入相同幅度的射频信号,并且在相位上2端口的射频信号超前3端口射频信号П/2,则射频功率在4端口输出并且功率为输入功率之和,在1端口由于信号抵消没有功率输出。

根据上述3 dB分支耦合器的传输特性,1端口入射的射频信号经过3 dB耦合器后,被平均分配到2个放大器芯片T1和T2的输入端口,其中2端口的射频信号超前3端口П/2。假设2个放大电路的特性完全一致,则放大器芯片T1和T2反射的射频信号幅度相同,反射信号将进入3 dB分支耦合器。由于反射信号在2端口的相位超前3端口П/2,按照3 dB分支耦合器的特性,合成功率在4端口输出被50 Ω的匹配电阻吸收,而在1端口则没有输出。因此,即使2个放大电路在输入端产生很大的反射,在平衡放大电路的射频输入端可以没有射频信号的反射,实现很低的输入驻波系数。同理,经过放大电路后的输出信号会在放大电路的输出端口合成,而反射信号则被50 Ω的匹配电阻吸收,可以大幅度降低放大电路的输出驻波系数。

2 放大器设计及优化

2.1 设计指标

频率范围:902 MHz~928 MHz;输入功率:19 dBm;输出功率:32 dBm;增益:13 dB;增益平坦度≤±0.5 dB;二次谐波分量≤-30 dBc;输入、输出驻波比≤1.5。

2.2 器件的选择

平衡功率放大器的设计需要2个3 dB正交耦合器和2个放大器芯片,由于电路结构完全对称,所以上下2个放大器芯片完全相同。3 dB正交耦合器的选择主要考虑其输入、输出驻波比。放大器芯片的选择主要考虑其1 dB增益压缩点。本设计选择了Anaren公司的3 dB正交耦合器XC0900A-03。该耦合器工作频段在811 MHz~1 000 MHz,驻波比都在1.5以下。放大器芯片为WJ公司的FP31QF,该放大器芯片的工作频段为50 MHz~4 000 MHz,在915 MHz时1 dB压缩点的输出功率可达34 dBm。上述器件的特性指标都满足设计要求,因此这些器件可以很好地应用在平衡功率放大器的设计中。

2.3 直流工作点的确定

在晶体管的技术参数中,半导体厂家通常会给出放大器芯片的直流工作电压和电流。本设计的放大器芯片FP31QF采用技术参数给定的(Vds=9 V,Ids=450 mA)直流工作点来设计直流偏置电路。

平衡功率放大器 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)