叠加偏置电流产生的动态功耗

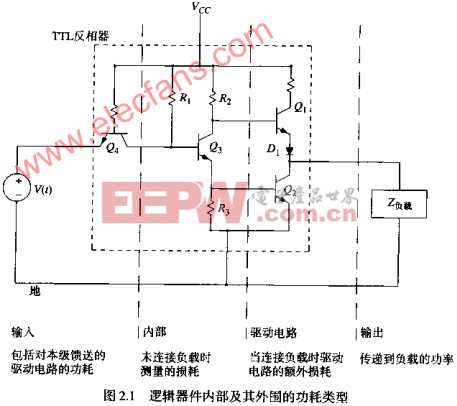

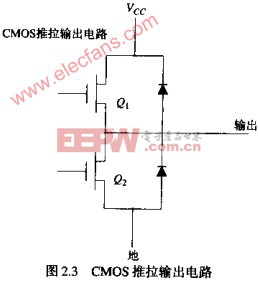

在图中2.1中,TTL反相顺的输出驱动电路在HI和LO之间交替转换,Q1或Q2交替处于导通状态,而不是两者同时导通。这种电路配置有两个激励电路,一个把输出电压上拉到HI,而另外一个把输出电压下拉到LO,通常称之为推拉输出电路。TTL和CMOS电路通常都有推拉输出电路。

图2.1中的二极管D1用来保证当晶体管Q3和Q2完全饱各时,输出电路箝位在LO状态,晶体管Q1将完全截止。这一特性可以防止Q2同时导通时而产生大电流。每个具有推拉输出电路的逻辑系列产品都有一些保护电路,以防止HI和LO输出驱动电路同时导通。

图2.1中描述的TTL驱动器电路的实验揭示了当电路从一个状态转换到另一个状态时,晶体管Q1和Q2可能在瞬间同时导通。任何重叠了的导通都将产生一个从VCC到地的浪涌电流,所消耗的功率以热量的形式消耗在晶体管Q1和Q2上。

肖特基TTL逻辑电路出现之前,一个TTL电路从LO转换到HI状态的过程中,在晶体管Q1开始导通后的一段时间内,晶体管Q2往往还维持在饱和状态,通过电阻R3释放其基极上存储的电荷。基极存储的这些电荷导致产生了一个固定时间的重叠。新的肖特基电路不再使晶体管Q2饱和,因此产生的重叠电流比较少。

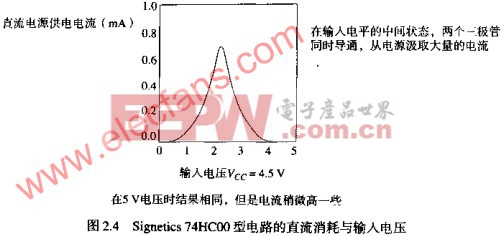

图2.3中描述的CMOS电路,在场效应晶体管Q1和Q2之间可能出现重叠导通,这取决于两个晶体管的临界栅-源极电压VCS、VCS参数的准确值很大程度上取决于制造过程,因此从个别CMOS器件得到的值概括出的经验是欠考虑的。图2.4标明了一个74HCOO门电路典型的直流电源电流与输入电压的函数关系典线。由于CMOS器件也存在叠加效应,减缓输入的转换时间往往会延长重叠时间。随着内部电路的响应变慢,在Q1和Q2都导通时的电压附近停留时间会更长。

对于一个快速的输入转换,重叠电流脉冲的大小和波形在每个周期都是一致的,并且每个周期消耗的能量也是相同的,因此由重叠偏置电流导致的额外功耗与转换速率成正比,与电容负载引起的功耗不同,由重叠驱动电流产生的功耗并不随电源电压的平方而增大。

如图2.4所示,74HC00电路的重叠电流与这个类型的门电路所能产生的最大驱动电流相比并不是很大。

对于TTL电路,叠加效应更显著。如果将一个TTL反相器的输入端连接到它自己的输出端,它将会自我偏置,从而进入叠加范围内,消耗大量能量。你能感觉到电路在发热。因此TTL电路不适合用做线性的小信号处理器件,因为它们在线性工作状态时要消耗额外的能量。相反,工作在重叠区域的射极耦合逻辑电路不会汲取额外的电流,可以用做优良的线性处理器件。

- 叠加偏置电流产生的动态功耗分析(06-06)

- 固态继电器的动态功耗和设计考量(01-24)

- 驱动容性负载的动态功耗分析(01-14)

- 推拉输出电路的动态功耗(06-12)

- 驱动容性负载的动态功耗(06-12)