TMS320F2812SPI接口设计

时间:06-13

来源:互联网

点击:

引言

目前,在一些控制系统中需要不断地调整参数或者改变相关的设置,才能取得良好的控制效果,并且将这些参数在掉电之前保存下来,从而确保下次运行时可以直接使用已经调整好的参数,而不必重新设置。这就需要EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦可编程只读存储器),一种掉电后数据不丢失的存储芯片,来存储这些数据。随着DSP芯片在控制系统中的应用越来越广泛,越来越多的控制系统采用DSP的SPI模块来对EEPROM进行操作,以实现数据的存储记录。

TMS320F2812是TI公司推出的一款用于控制系统的高性能、多功能、高性价比的32位定点DSP芯片。TMS320F2812采用哈佛总线结构,具有密码保护机制,可在一个周期内进行双16×16乘加和32×32乘加操作,从而兼顾控制和快速运算的双重功能;芯片上集成了多种外设,尤其是2个事件管理器为电动机以及功率变换控制提供了很大的便利,因此在控制系统中得到了很广泛的应用。下面以Microchip公司的EEPROM 25LC040为例,介绍TMS320F2812的SPI接口设计。

1主要芯片简介

1.1TMS320F2812 SPI模块

SPI总线是一种同步串行外设接口,它可以使控制芯片以串行方式与各种外围设备进行通信。该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和片选信号STE。

TMS320F2812的SPI模块有主从两种工作模式,可以通过寄存器来设置(其数据长度可以配置为1~16位,具有125种可编程的波特率);通过时钟极性和时钟相位可以将SPI模块配置成4种不同的时钟模式;有16级发送/接收FIFO,并且具有延时发送的功能,可以通过中断或者查询的方式来完成数据的发送和接收。

SPI模块有8个寄存器需要设置,用来控制SPI的操作:SPICCR、SPICTL用来配置SPI的工作状态;SPISTS用来获取SPI的状态信息,包括2个接收状态位和1个发送缓冲状态位,可以通过查询这些状态位来判断是否完成数据的接收或者发送;SPIBRR用来设置SPI的波特率;SPIRXBUF和SPITXBUF分别用来接收和发送数据;SPIDAT装载SPI要发送的数据,SPIPRI用来设置SPI中断的优先级。

1.2EEPROM芯片25LC040

25LC040是SPI接口的4 Kb EEPROM,至少可以擦写1 000万次,数据至少可以保存200年,可以满足大部分数据存储的要求。DSP必须能通过相应的指令实现对25LC040的访问。25LC040的操作指令如表1所列。

表1中,A8是读/写开始地址的第9位。25LC040是512×8位的EEPROM,分成上下两页,每页256个字节,通过选择A8可以实现对不同页的操作。

1.2.1读时序

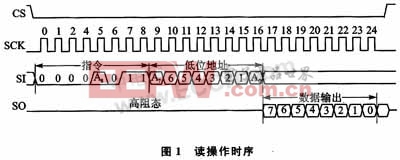

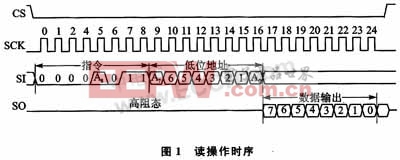

当片选信号为低时,向25LC040传送8位的读指令(0000 A8011),紧接着传送需要读取数据的低8位地址。当正确的读写指令和地址被识别后,EEPROM中对应地址的数据将会由输出引脚顺次传出,若继续提供时钟信号,下一位地址对应的数据也会依次读出。当片选信号为高时,读数据的操作将会被终止。其具体操作如图1所示。图中,CS为片选信号,SCK为时钟信号,SI为输入引脚信号,SO为输出引脚信号。

1.2.2写时序

在对25LC040进行任何写操作之前,必须先执行WREN(写使能)指令。写使能指令的操作如图2所示。先使片选信号为低,然后传送写使能指令到25LC040中,指令传送完毕后,必须将片选信号设置为高以完成写使能操作。如果写指令传送结束后没有拉高片选信号,直接进行写操作,那么数据将不会写入到存储阵列中。

写使能操作完成后,片选信号应该被拉低以进行写操作,时序如图3所示。写指令、写入地址以及写入的数据会被依次传送到25LC040中。若要使数据正确地写入到存储阵列中,片选信号应该在最后一个有效字节的D0位传送完毕后被拉高。

2TMS320F2812的SPI接口设计

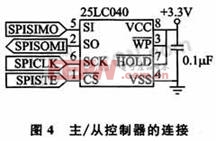

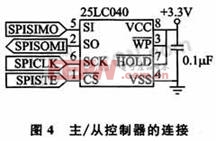

TMS320F2812与25LC040的硬件连接如图4所示。TMS320F2812工作在主模式,SPISIMO为主模式下的数据输出接口,连接到25LC040的数据接收端口;SPISOMI为主模式下的数据输入接口,连接到25LC040的数据发送端口;时钟信号SPICLK和片选信号SPISTE均由TMS320F2812产生。写保护引脚WP直接接高电平以确保25LC040总是可以被写入。

2.1 SPI模块的设置

SPI模块的波特率可由如下两种情况计算得出:

①SPIBRR=3~127,波特率的计算公式为:

SPI波特率=LSPCLK/(SPIBRR+1)

②SPIBRR=0~2,波特率的计算公式为:

SPI波特率=LSPCLK/4

LSPCLK是TMS320F2812的低速外设时钟频率;SPIBRR是SPIBRR寄存器的值。将LSPCLK设置成37.5 MHz,25LC040的最大时钟频率为2 MHz,SPI的波特率应该小于2 MHz,即37.5/(SPIBRR+1)≤2,SPIBRR的取值范围为SPIBRR≥18。

通信中将SPISIMO、SPISOMI和SPICLK设置为基本功能SPI口,SPISTE设置为一般I/O口。作为25LC040的片选信号,当主/从控制器进行数据交换时,SPISTE配置成低电平,数据传输结束后再配置成高电平。

TMS320F2812的数据寄存器都是16位的,且接收和发送都是双缓冲的,而25LC040的地址和数据寄存器都是8位的,因此将SPI模块的数据长度设置成8位。发送缓冲寄存器SPITXBUF中的数据以左对齐的方式发送,先发送数据的最高位,因此在发送数据前必须将等待发送的数据放在SPITXBUF的高8位。当要对25LC040进行写使能操作时,写入SPITXBUF的数据应为0x0600。TMS320F2812则是以右对齐的方式来接收数据的,8位的数据被放在SPITXBUF的低8位上。

SPI模块有4种时钟模式:上升沿无延时模式、上升沿有延时模式、下降沿无延时模式和下降沿有延时模式。25LC040是在时钟的上升沿接收数据,下降沿发送数据,所以TMS320F2812的SPI应该配置为上升沿发送数据,下降沿接收数据。

2.2接收数据流程

通过SPI读取数据比较简单,只需要依次传送读指令和待读数据的低位地址,就可以在SPISOMI引脚上接收到25LC040中的数据。因为TMS320F2812为主控制器,所以必须先发送一个无意义的数,才能够启动时钟。在SPI状态寄存器(SPISTS)中有一个SPI中断标志位(SPIINT FLAG),该位是一个只读标志位,由硬件设置。当SPI已经完成数据发送或者接收,正在等待下一步的操作时,SPI中断标志位被置1,若使能SPI中断,将产生一个SPI中断请求。可以通过查询SPI中断标志位来判断数据是否完成接收。若该标志为1,已接收的数据将被放入接收缓冲寄存器SPIRXBUF中,通过读SPIRXBUF寄存器即可得到需要的数据。下面给出接收数据的子程序,其中addr为待读数据的低位地址。

2.3发送数据流程

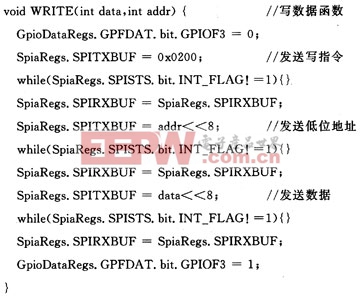

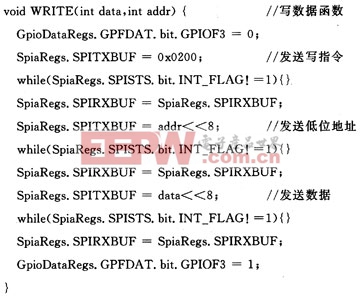

SPI发送数据需要先完成写使能操作,然后依次传送写指令和低位地址,才可以正确地进行数据写入。向SPITXBUF寄存器中写入待发的数据,SPI时钟就会自动启动,数据会由输出引脚顺次传出;数据传送完后,SPI时钟自动停止。也可以通过查询SPI中断标志位来判断数据是否完成发送,若该标志位为1,则可接着发送下一个数据。SPI设置成主模式时,发送完一个数据,必须要空读一下SPIRXBUF寄存器,以清除SPI中断标志位。由于在读取数据的过程中已经包含读SPIRXBUF寄存器,因此在读取数据时不需要再空读SPIRXBUF寄存器。下面给出发送数据程序,其中data为待发送的数据,addr为待发送数据将要存放的地址。

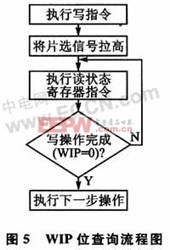

2.4运行效率的提升

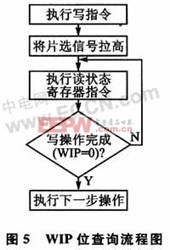

25LC040要求在写操作之后有一定的写周期时间来存储数据,其间TMS320F2812对25LC040的所有访问会被忽略。每个器件都有规定的最坏情况写周期时间,可以通过在再次访问25LC040之前插入不小于最坏情况写周期时间的延时等待来确保遵守写周期时间。但是25LC040常常会在最大规定时间内完成写周期,而此时TMS320F2812还在等待,会造成不必要的时间浪费。25LC040内部有一个状态寄存器,其第1位为WIP(Write-In-Process)位,该位是一个只读位,可以显示25LC040是否处在写周期内。当芯片处于写周期时,WIP位置1;当写操作完成时,WIP位立即清零。状态寄存器在写操作期间仍然可读,可以通过读状态寄存器指令(WRSR)来获取状态寄存器的内容,从而得到WIP位的值以判断写周期何时完成,以进入下一步操作。这样就可以减少不必要的等待时间,使运行更加高效。具体的流程如图5所示。

结语

本文在分析TMS320F2812 SPI模块的特点的基础上,描述了SPI各个控制寄存器的作用。通过与EEPROM25LC040通信的实例,给出了SPI口的软硬件设计方法,并对其中需要注意的关键问题进行了分析讨论。

目前,在一些控制系统中需要不断地调整参数或者改变相关的设置,才能取得良好的控制效果,并且将这些参数在掉电之前保存下来,从而确保下次运行时可以直接使用已经调整好的参数,而不必重新设置。这就需要EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦可编程只读存储器),一种掉电后数据不丢失的存储芯片,来存储这些数据。随着DSP芯片在控制系统中的应用越来越广泛,越来越多的控制系统采用DSP的SPI模块来对EEPROM进行操作,以实现数据的存储记录。

TMS320F2812是TI公司推出的一款用于控制系统的高性能、多功能、高性价比的32位定点DSP芯片。TMS320F2812采用哈佛总线结构,具有密码保护机制,可在一个周期内进行双16×16乘加和32×32乘加操作,从而兼顾控制和快速运算的双重功能;芯片上集成了多种外设,尤其是2个事件管理器为电动机以及功率变换控制提供了很大的便利,因此在控制系统中得到了很广泛的应用。下面以Microchip公司的EEPROM 25LC040为例,介绍TMS320F2812的SPI接口设计。

1主要芯片简介

1.1TMS320F2812 SPI模块

SPI总线是一种同步串行外设接口,它可以使控制芯片以串行方式与各种外围设备进行通信。该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和片选信号STE。

TMS320F2812的SPI模块有主从两种工作模式,可以通过寄存器来设置(其数据长度可以配置为1~16位,具有125种可编程的波特率);通过时钟极性和时钟相位可以将SPI模块配置成4种不同的时钟模式;有16级发送/接收FIFO,并且具有延时发送的功能,可以通过中断或者查询的方式来完成数据的发送和接收。

SPI模块有8个寄存器需要设置,用来控制SPI的操作:SPICCR、SPICTL用来配置SPI的工作状态;SPISTS用来获取SPI的状态信息,包括2个接收状态位和1个发送缓冲状态位,可以通过查询这些状态位来判断是否完成数据的接收或者发送;SPIBRR用来设置SPI的波特率;SPIRXBUF和SPITXBUF分别用来接收和发送数据;SPIDAT装载SPI要发送的数据,SPIPRI用来设置SPI中断的优先级。

1.2EEPROM芯片25LC040

25LC040是SPI接口的4 Kb EEPROM,至少可以擦写1 000万次,数据至少可以保存200年,可以满足大部分数据存储的要求。DSP必须能通过相应的指令实现对25LC040的访问。25LC040的操作指令如表1所列。

表1中,A8是读/写开始地址的第9位。25LC040是512×8位的EEPROM,分成上下两页,每页256个字节,通过选择A8可以实现对不同页的操作。

1.2.1读时序

当片选信号为低时,向25LC040传送8位的读指令(0000 A8011),紧接着传送需要读取数据的低8位地址。当正确的读写指令和地址被识别后,EEPROM中对应地址的数据将会由输出引脚顺次传出,若继续提供时钟信号,下一位地址对应的数据也会依次读出。当片选信号为高时,读数据的操作将会被终止。其具体操作如图1所示。图中,CS为片选信号,SCK为时钟信号,SI为输入引脚信号,SO为输出引脚信号。

1.2.2写时序

在对25LC040进行任何写操作之前,必须先执行WREN(写使能)指令。写使能指令的操作如图2所示。先使片选信号为低,然后传送写使能指令到25LC040中,指令传送完毕后,必须将片选信号设置为高以完成写使能操作。如果写指令传送结束后没有拉高片选信号,直接进行写操作,那么数据将不会写入到存储阵列中。

写使能操作完成后,片选信号应该被拉低以进行写操作,时序如图3所示。写指令、写入地址以及写入的数据会被依次传送到25LC040中。若要使数据正确地写入到存储阵列中,片选信号应该在最后一个有效字节的D0位传送完毕后被拉高。

2TMS320F2812的SPI接口设计

TMS320F2812与25LC040的硬件连接如图4所示。TMS320F2812工作在主模式,SPISIMO为主模式下的数据输出接口,连接到25LC040的数据接收端口;SPISOMI为主模式下的数据输入接口,连接到25LC040的数据发送端口;时钟信号SPICLK和片选信号SPISTE均由TMS320F2812产生。写保护引脚WP直接接高电平以确保25LC040总是可以被写入。

2.1 SPI模块的设置

SPI模块的波特率可由如下两种情况计算得出:

①SPIBRR=3~127,波特率的计算公式为:

SPI波特率=LSPCLK/(SPIBRR+1)

②SPIBRR=0~2,波特率的计算公式为:

SPI波特率=LSPCLK/4

LSPCLK是TMS320F2812的低速外设时钟频率;SPIBRR是SPIBRR寄存器的值。将LSPCLK设置成37.5 MHz,25LC040的最大时钟频率为2 MHz,SPI的波特率应该小于2 MHz,即37.5/(SPIBRR+1)≤2,SPIBRR的取值范围为SPIBRR≥18。

通信中将SPISIMO、SPISOMI和SPICLK设置为基本功能SPI口,SPISTE设置为一般I/O口。作为25LC040的片选信号,当主/从控制器进行数据交换时,SPISTE配置成低电平,数据传输结束后再配置成高电平。

TMS320F2812的数据寄存器都是16位的,且接收和发送都是双缓冲的,而25LC040的地址和数据寄存器都是8位的,因此将SPI模块的数据长度设置成8位。发送缓冲寄存器SPITXBUF中的数据以左对齐的方式发送,先发送数据的最高位,因此在发送数据前必须将等待发送的数据放在SPITXBUF的高8位。当要对25LC040进行写使能操作时,写入SPITXBUF的数据应为0x0600。TMS320F2812则是以右对齐的方式来接收数据的,8位的数据被放在SPITXBUF的低8位上。

SPI模块有4种时钟模式:上升沿无延时模式、上升沿有延时模式、下降沿无延时模式和下降沿有延时模式。25LC040是在时钟的上升沿接收数据,下降沿发送数据,所以TMS320F2812的SPI应该配置为上升沿发送数据,下降沿接收数据。

2.2接收数据流程

通过SPI读取数据比较简单,只需要依次传送读指令和待读数据的低位地址,就可以在SPISOMI引脚上接收到25LC040中的数据。因为TMS320F2812为主控制器,所以必须先发送一个无意义的数,才能够启动时钟。在SPI状态寄存器(SPISTS)中有一个SPI中断标志位(SPIINT FLAG),该位是一个只读标志位,由硬件设置。当SPI已经完成数据发送或者接收,正在等待下一步的操作时,SPI中断标志位被置1,若使能SPI中断,将产生一个SPI中断请求。可以通过查询SPI中断标志位来判断数据是否完成接收。若该标志为1,已接收的数据将被放入接收缓冲寄存器SPIRXBUF中,通过读SPIRXBUF寄存器即可得到需要的数据。下面给出接收数据的子程序,其中addr为待读数据的低位地址。

2.3发送数据流程

SPI发送数据需要先完成写使能操作,然后依次传送写指令和低位地址,才可以正确地进行数据写入。向SPITXBUF寄存器中写入待发的数据,SPI时钟就会自动启动,数据会由输出引脚顺次传出;数据传送完后,SPI时钟自动停止。也可以通过查询SPI中断标志位来判断数据是否完成发送,若该标志位为1,则可接着发送下一个数据。SPI设置成主模式时,发送完一个数据,必须要空读一下SPIRXBUF寄存器,以清除SPI中断标志位。由于在读取数据的过程中已经包含读SPIRXBUF寄存器,因此在读取数据时不需要再空读SPIRXBUF寄存器。下面给出发送数据程序,其中data为待发送的数据,addr为待发送数据将要存放的地址。

2.4运行效率的提升

25LC040要求在写操作之后有一定的写周期时间来存储数据,其间TMS320F2812对25LC040的所有访问会被忽略。每个器件都有规定的最坏情况写周期时间,可以通过在再次访问25LC040之前插入不小于最坏情况写周期时间的延时等待来确保遵守写周期时间。但是25LC040常常会在最大规定时间内完成写周期,而此时TMS320F2812还在等待,会造成不必要的时间浪费。25LC040内部有一个状态寄存器,其第1位为WIP(Write-In-Process)位,该位是一个只读位,可以显示25LC040是否处在写周期内。当芯片处于写周期时,WIP位置1;当写操作完成时,WIP位立即清零。状态寄存器在写操作期间仍然可读,可以通过读状态寄存器指令(WRSR)来获取状态寄存器的内容,从而得到WIP位的值以判断写周期何时完成,以进入下一步操作。这样就可以减少不必要的等待时间,使运行更加高效。具体的流程如图5所示。

结语

本文在分析TMS320F2812 SPI模块的特点的基础上,描述了SPI各个控制寄存器的作用。通过与EEPROM25LC040通信的实例,给出了SPI口的软硬件设计方法,并对其中需要注意的关键问题进行了分析讨论。

- 基于DSP的全桥移相控制感应加热电源研究(01-04)

- 一种提高TMS320F2812 ADC精度的方法(08-23)

- 有源电力滤波器中的谐波检测电路设计(01-14)

- 基于TMS320F2812控制的有源电力滤波器研制(01-26)

- 一种基于DSP芯片与CAN总线的电源监控系统设计(03-23)

- 基于DSP技术的5kW离网型光伏逆变器设计(05-30)