怎样提高数字定位器的带宽

字串9

字串9

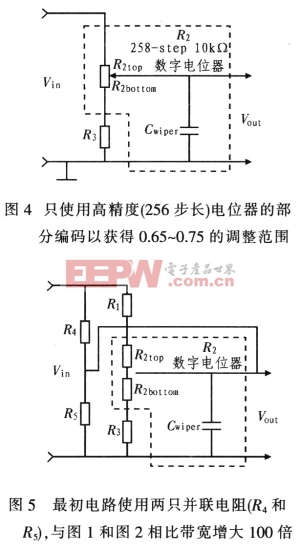

与32步长电位器相比,该方法的缺点是256步长电位器成本较高,故可选用封装尺寸较大的电位器。假设Cwiper为30 pF,VOUT/VIN=0.70,处于调整范围的中点,图4电路中有384 kHz的-0.1 dB带宽,879 kHz的-0.5 dB带宽,2.52 MHz的一3dB带宽。与表1相比,其带宽提高3倍。另一种成本更低、性能更好的方案是在图图5最初电路使用两只并联电阻(R4和l电路中加入分立电 R5),与图l和图2相比带宽增大100倍阻,如图5所示。 字串3

7 使用并联电阻降低电路阻抗

电路中增加并联电阻(注意,使用图2中引入的数字电位器模型)。降低电路阻抗(提高带宽),通过设置电路增益,限制由数字电位器在0编码到满标编码之间摆动时导致的衰减,可以达到双重目的。

字串1

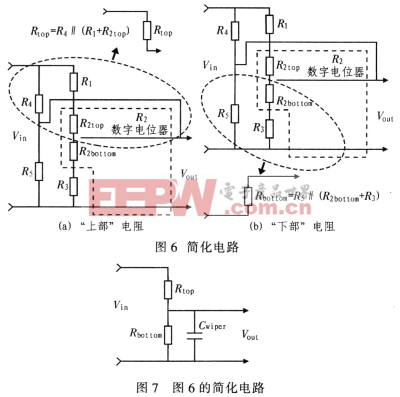

设置电位器电路增益,使用并联器件限制其调整范围(R4和R5,而不是简单串联R1、R2和R3),其电路带宽优于图1带宽。还需要注意,电阻R1、R2和R3还会影响电路增益,但由于其串联电阻要比R4和R5大得多,这种影响非常小。可以通过简单示例来说明R4和R5对图5电路的影响。在图6(a)中,电路上部电阻采用了图中方程给出的电阻组合值。注意,由于R4是与R1和R2top并联,它降低了电路阻抗。

字串2

字串2

在图6(b)中,电路下部电阻采用了图中方程给出的电阻组合值。注意,由于R5是与R3和R2bottom并联,降低了电路阻抗。正是较低的电路阻抗使得带宽大大提高,达到设计目标的要求。图7结合了图6中的简化示例,给出了VOUT/VIN传输函数。从该图中可以清楚看到,通过降低电路阻抗(R2top小于R1+R2top,R2bottom小于R2bottom+R3),提高了电路带宽。 字串6

8 实际值

实际设置R1、R3、R4和R5的阻值,可以对比图l电路的带宽,从而确定R4和R5对电路性能的影响。使用图6(b)中的方程,得出R1、R3、R4和R5的阻值,然后计算最终带宽。使用表格,可以找到满足图6(b)中方程的元件值:R1=3.48 kΩ、R2=10 kΩ、R3=4.53 kΩ、R4=l kΩ、R5=2.8 kΩ。采用这些元件值得出了表2所列的带宽。注意,这些结果要比图1电路提高100倍。 字串1

字串7

字串7

*注意,带宽与触点电容成反比。例如,采用3 pF Cwiper,带宽提高3.3倍。

字串9

9 结语

介绍了在窄带数字电位器中简单加入并联电阻以提高系统带宽的方法,显著提高系统性能(带宽可提高100倍)。设计前提是假设实际应用允许降低电位器的控制范围,以提高带宽。带宽提高后,数字电位器可用于以前无法涉及的高频领域,例如视频信号链路控制等。■

字串6

- 锁相环相位噪声与环路带宽的关系分析(08-04)

- 电流反馈运放大器工作原理的问题(11-07)

- 基于高速多通道CCD预放电路的设计方案(10-25)

- 高速信号发生应用中的关键要求(11-04)

- 适用于可见光通信的LED器件(01-12)

- 对目前的紧凑型设计而言,过去的经验法则可能不再是最佳解决方案(11-24)