增益为1/2的差分输出放大器系统

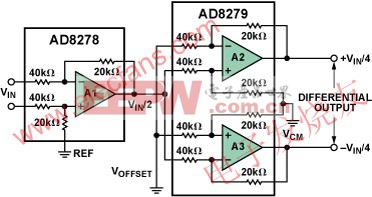

采用小尺寸工艺设计的高性能ADC通常采用1.8V至5V单电源或±5V双电源供电。为了处理±10 V或更大的实际信号,ADC一般前置一个放大器以衰减该信号,防止ADC输入端出现饱和或受损。这种放大器通常具有单端输出,但为了获得差分输入ADC的全部优势,包括更高动态范围、更佳共模抑制性能和更低的噪声敏感度,具有差分输出会更有利。图1显示一个增益为1/2的差分输出放大器系统。

图1. G = 1/2的差分输出差动放大器功能框图

差分放大器A1的增益配置为1/2。此放大器的输出送到放大器A2的同相输入端和放大器A3的反相输入端。放大器A2和A3也以增益1/2工作,二者的输出180度反相,构成一路差分输出。差分输出电压VOUT A2–VOUT A3等于VIN/4–(–VIN/4),或者VIN/2的总差分输出电压,正如希望的那样。

VOFFSET 引脚可用来偏移输出从而提高ADC的动态范围。从VOFFSET到输出端的差分增益为–1。如果不需要偏移调整,应将此节点接地。

VCM 引脚设置差分输出的共模电压。这在驱动单电源ADC时特别有用,可以将电路的共模输出设置到中间电源电压。从VCM 到输出端的增益为1。如果不需要共模调整,应将此节点接地。

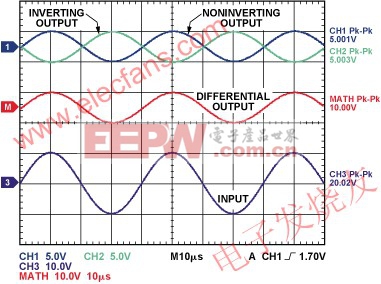

图2显示该电路的性能。输入为25kHz、20V峰峰值正弦波。通道1为同相输出,通道2为反相输出,通道3为输入。Math通道为两路输出之差。每路输出均为输入信号的1/4,两路输出彼此反相,因此其差值为输入信号的1/2。

图2. 差分输出为输入信号的1/2

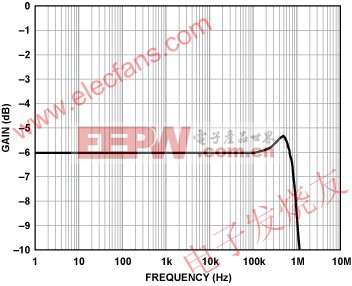

图3显示该电路增益与频率响应的关系,证明它很稳定,在1MHz带宽内的峰化小于1dB。

图3. 差分输出差动放大器的频率响应

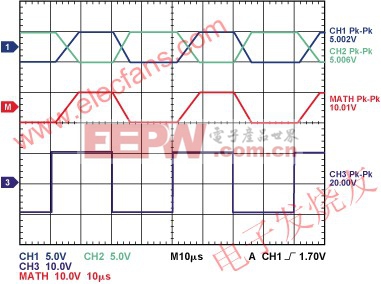

图4表明,该电路对大方波输入的响应没有可观的过冲,建立时间非常快。因为各放大器仅携带一半的信号,所以差分输出压摆率是单个输出的两倍。

图4. 差分输出差动放大器的大信号性能

双通道差动放大器AD8279 采用14引脚窄体SOIC封装。AD8278 采用8引脚MSOP封装。经过激光调整的精密电阻集成在放大器的同一芯片上,因此其失调、增益、共模误差和温度漂移非常小,构成一个高精度系统。虽然AD8278 (200 µA)和AD8279(每个放大器200 µA)的功耗很低,但该系统具有1MHz的带宽和2.4V/µs的压摆率。AD8278和AD8279可以在2.5V单电源至±18V双电源的极宽电源电压范围内工作。输入摆幅可以大大超出电源轨,因而该系统可以在有大共模电压和噪声的情况下测量大信号(±20 V或以上),堪称高性能、低压ADC的理想前端。

- 一种增大放大器增益的方法(11-28)

- 改善可编程增益放大器性能的一个技巧(05-21)

- 运用负反馈模型分析实际运算放大器电路(05-07)

- 在数据转换系统中校准增益误差的方法(03-23)

- 一个对温度不敏感的高增益运算放大器设计(09-16)

- 增益天线种类详解(11-12)