双极发射极跟随器:具有双通道反馈的RISO

着Aol曲线下降。

|

| 图17:FB#2图解分析:发射极跟随器。 |

|

| 图18:双通道反馈、叠加以及1/β:发射极跟随器。 |

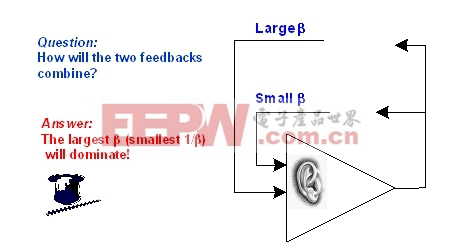

图18告诉我们,当整个运算放大器电路采用双通道反馈电路时,最大的β值电路将居支配地位。一个很明显的例子就是,如果有两个人对着您的同一只耳朵讲话,您会更易于听到哪个人的讲话?当然是嗓门最大的那个人!同样的道理,运算放大器也将会“听到”β值最大或1/β值最小的反馈电路。运算放大器察觉到最终的1/β曲线将是在各种FB#1 1/β或FB#2 1/β频率时,频率较低的那一条曲线。

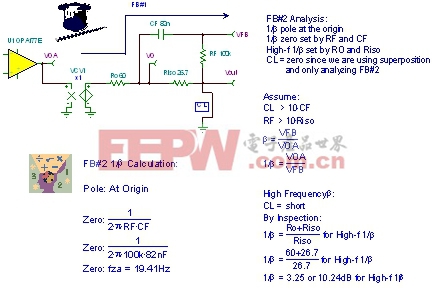

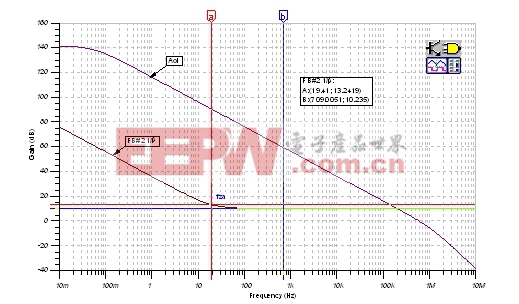

如图19所示,里面会有一些主要的假设。我们将这些假设运用于几乎所有的具有双通道反馈的RISO电路中。首先,我们假设CL>10*CF,这也就是说,在高频率时,CL早在CF短路前短路。因此,我们将短路CL以排除FB#1,从而便于单独分析FB#2。另外,我们假设RF>10*Riso,这意味着作为Riso的负载,该RF几乎完全失效。从图19和图20中具体的公式推导,我们可以看出,当zero,fza=19.41Hz(由RF和CF产生)时,FB#2在原点拥有一个极点。由于在高频时,CF和CL同时处于短路状态,所以FB#2高频1/β部分即为Ro+Riso与Riso之间的比值。FB#2 1/β的公式推导请参阅下一张图(图20),有关计算结果请参阅下图。FB#2高频1/β设置为3.25dB或10.24dB、原点拥有一个极点以及当频率为19.41Hz时的零点。

|

| 图19:FB#2分析:发射极跟随器。 |

|

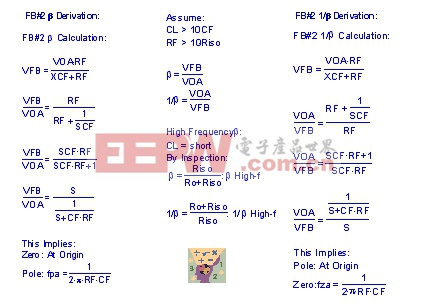

| 图20:FB#2 1/β公式推导:发射极跟随器。 |

FB#2β的公式推导如图20左侧所示。由于1/β是β的倒数,所以FB#1 1/β的计算结果可以轻而易举的被推导出来,具体推导过程请参阅图20右侧。从图中我们还发现,在β推导过程中的pole,fpa变成了1/β推导过程中的zero,fza。

|

| 图21:FB#2AC电路分析:发射极跟随器。 |

|

| 图22:FB#2 1/β曲线:发射极跟随器。 |

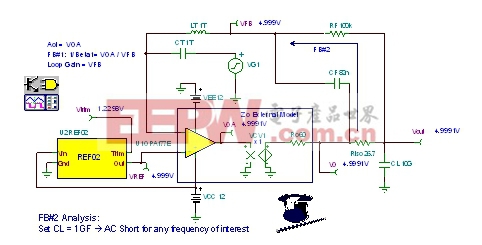

为了检验FB#2的一阶分析情况,我们可采用如图21所示的Tina SPICE电路。再者,为了便于分析,我们将CL设置为10GF,因此对各种相关的频率而言,CL都等同于短路状态。但是,在开展AC分析前,仍允许SPICE查找到相应的DC工作点。

Tina SPICE仿真的结果如图22所示。FB#2 1/β曲线正如当fza=19.41Hz以及高频1/β=10.235dB时,采用一阶分析推算出来的结果一样。另外,我们也绘制出OPA177 Aol曲线,以弄清楚在高频率时,FB#2将如何与其相交。

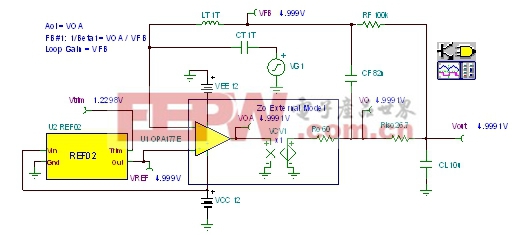

如果推算的FB#1和FB#2的叠加结果会产生所需的最终1/β曲线,那么我们将通过如图23所示的Tina SPICE电路,开展分析工作。我们还可通过Tina SPICE电路,绘制出Aol曲线、最终的1/β曲线以及环路增益曲线。

| 图23:最终环路增益分析电路:发射极跟随器。 |

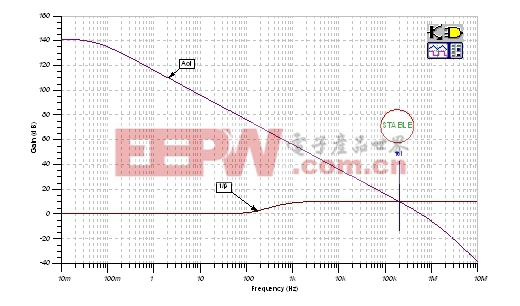

从图24中,我们可以看出,分析结果验证了我们所推算的最终1/β曲线。在环路增益为零的fcl处,推算的接近速率为20dB/decade。

|

| 图24:最终1/β曲线:发射极跟随器。 |

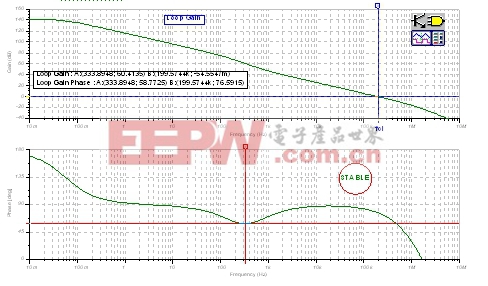

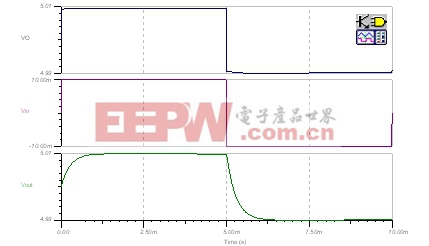

最终电路的环路增益相位曲线(采用FB#1和FB#2)如图25所示。相移从未下降至58.77度以下(如为当频率为199.57kHz时的情况),而且,在fcl处(频率为199.57kHz),相位裕度为76.59度。

|

| 图25:最终环路增益分析:发射极跟随器。 |

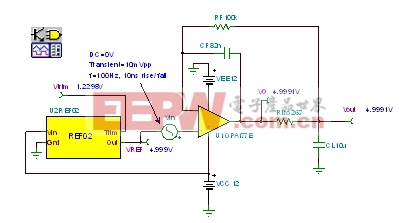

我们将采用图26中的Tina SPICE电路,对我们的稳定电路进行最后的检验-瞬态稳定性测试。

|

| 图26:最终瞬态稳定性测试电路:发射极跟随器。 |

|

| 图27:最终瞬态稳定性测试:发射极跟随器。 |

|

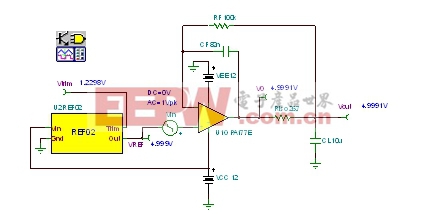

通过图28中的Tina SPICE电路,可验证我们对Vout/Vin的推算是否正确。

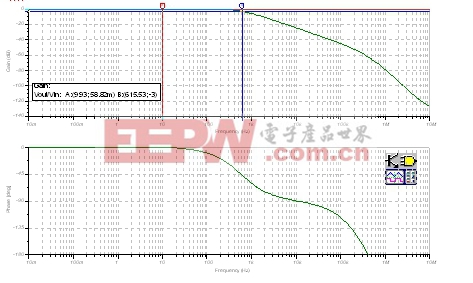

从图29中,我们可以看出,Vout/Vin的测试结果与我们推算的一阶分析结果一致,具体表现为:当频率为625.53Hz时,单极点开始下降。而且,当频率约为200kHz(此时,FB#2与OPA177 Aol曲线相交)时,出现第二个极点。

|

| 图29:最终Vout/Vin传输函数:发射极跟随器。 |

图30总结了一种易于使用的渐进式程序。这种程序轻松地将具有双通道反馈的RISO电容性负载稳定性技术应用于双极发射极跟随器输出运算放大器上。

1. 测量运算放大器的Aol。

2. 测量运算放大器的Zo,并在图上绘制出其曲线。

3. 确定RO。

4. 创建Zo的外部模型。

5. 计算FB#1低频1/b:对单位增益电压缓冲器而言,该值为1。

6. 将FB#2高频1/b设置为比FB#1低频1/b高+10dB(为获得最佳的Vout/Vin瞬态响应并实现环路增益带宽相移量最少)。

7. 从FB#2高频1/b中选择Riso以及RO。

8. 从CL、Riso、RO中,计算FB#1 1/bfzx。

9. 设置FB#2 1/b fza=1/10fzx。

10. 选择具有实际值的RF和CF,以产生fza。

11. 采用Aol、1/b、环路增益、Vout/Vin以及瞬态分析的最终值,运行仿真以验证设计的可行性。

12. 核实环路增益相移的下降不得超过135度(>45度相位裕度)。

13. 针对低噪声应用而言:检查Vout/Vin扁平响应,以避免增益骤增→Vout/Vin中的噪声陡升。

- 双极性移相控制高频脉冲交流环节逆变器研究(10-07)

- 一种单片机双极模拟信号A/D转换的电路设计(06-08)

- 一种H型双极模式PWM控制的功率转换电路设计(11-24)

- 用于军事和航空航天领域的高可靠性技术(06-24)

- 横向PNP钳位型晶体管受辐射时损耗的计算(12-29)

- 选择开关电源双极性开关管的方法(05-29)