高精度时钟发生器MAX945x的元件选择和性能测试

时间:04-14

来源:互联网

点击:

引言

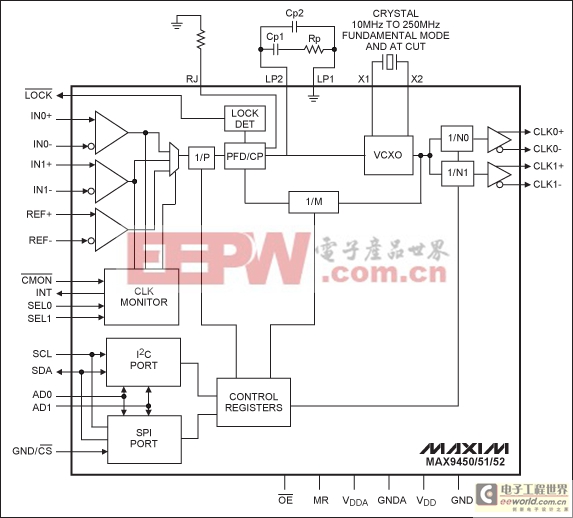

MAX9450/MAX9451/MAX9452时钟发生器1可以产生高精度时钟,为SONET/SDH系统、千兆位以太网和3G基站的ADC/DAC提供定时。该器件还可以作为抖动抑制器使用,并且LVPECL、HSTL和LVDS三种不同输出类型具有相同的内核。芯片的结构框图如图1所示。

图1. MAX9450/MAX9451/MAX9452的结构框图

MAX945x内集成的VCXO可以省去外部VCXO,提供高性价比的精密时钟方案。VCXO频率和调谐范围由外部晶体的参数决定。VCXO的设计保证其可以配合15MHz到160MHz的宽频率范围晶体工作。与寻找恰当频率的VCXO相比,相同频率的晶体更容易获得,这为不同的应用提供了灵活性。这些器件的分频范围非常广泛,可以从1到32,768,这允许时钟发生器的160MHz输出同步至8kHz参考输入。并且器件具有参考监视功能,可以监视输入参考时钟的质量。

为了正确使用这些芯片,设计者必须选择适当的晶体和环路滤波器元件。本应用笔记指导如何选择这些外部元件。同时提供了使用多种晶体时的性能测试结果。

晶体选择

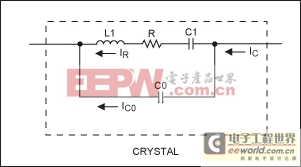

如图1所示,VCXO的有源电路都集成在芯片内部,外部只有晶体和环路滤波器的RC元件。按照上文提示,晶体频率必须与所要求的输出频率相同。但是我们同样需要考虑晶体的振动模式、切割类型、负载电容(CL)、频率公差范围、静电容(C0)和动态电容(C1)。MAX945x使用的晶体必须是AT切割,基频谐振模式,这意味着晶体需要具有较宽的调谐范围和较小的温度漂移。Maxim的应用笔记2127,"Modeling of Quartz Crystal",分析了晶体的等效电路(图2)。

图2. 晶体等效电路

VCXO的振荡频率由以下公式决定:

由这个等式,我们得到fP相对CL变化的微分解析:

由等式2可以发现,调谐灵敏度随着C1值的增大、C0和CL的减小而增大。因此,为了使MAX945x时钟发生器具有较宽的调谐范围,需要选择具有相同C1、C0和CL相对值的晶体。实验证明,为了得到良好的调谐范围,需要选择C1 > 6fF, CL = 8pF, C0 2.5pF (这将由随后的数据说明)。值得注意的是,如果CL的值小于8pF,将在调谐范围的正段带来损失。我们测试了KDS (www.kds.info/index_en.htm)2的DSX321S晶体和Fortiming (www.4timing.com)3的XHFF45晶体,测试结果将在下文描述。对于两次晶体测试,PCB上使用的并联电容数值在表1中给出。

环路滤波器元件选择

MAX9450具有外部环路滤波器,可以为PLL环路滤波器的元件设置提供灵活性。选择环路滤波器的带宽有一个通用规则:为了抑制由参考输入带来的抖动,应选择较窄的PLL带宽;为了抑制由VCXO带来的抖动,应使用较宽的PLL带宽。因此,通常假设VCXO的抖动远小于参考输入的抖动带宽,然后再确定恰当的PLL滤波器带宽。在本例中PLL滤波器带宽应比参考输入抖动带宽窄。然而在实际应用中,我们通常不知道参考输入的抖动带宽和VCXO的抖动程度。因此,最佳的环路滤波器元件经常是通过了解元件如何影响PLL带宽,再由实验的方法来确定。可以看到开环单位增益带宽ωo和PLL的3dB带宽ω3db相同。这意味着ωo可以由PLL的抖动衰减需求来确定。下面的公式给出如何由已知的ωo来推来导元件选择。ωo可以表达为:

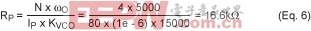

这里IP是电荷泵电流,RP是环路滤波器电阻,N是分频比,KVCO是VCXO的灵敏度。此等式成立的条件是RPCP1的时间常数满足:

此外,该关系式确保了足够的相位裕量来保持环路稳定性。CP2的作用是滤除电流电荷泵开关时的纹波电压。选择CP2的通用规则是:

通过实例来计算元件的数值,将有助于理解。假设ω3db的期望值为5000rad/S,N = 4,IP = 80μA。KVCO的测量值平均为15kHz/V。由等式3可得:

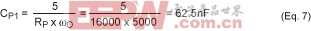

选择RP = 16kΩ。因此CP1的数值可由下式确定:

按照等式5,选择CP1 = 66nF,CP2 = 6.6nF。为了得到指定的80μA电荷泵电流,利用MAX9450数据资料中第10页的公式,1可得到RJ的数值为30kΩ。欲了解选择环路滤波器元件的完整讨论,请阅读本文最后的参考文献。4

测量结果

我们测试了KDS和Fortiming的晶体。表1显示了晶体的调谐范围和MAX9450的抖动性能。并没有对每一个晶体都进行抖动测试;周期抖动用有效值和峰峰值表示。相位噪声在12kHz到20MHz带宽内进行测量。表1. MAX9450的调谐范围和抖动性能

| KDS Crystal DSX321S | ||||||

| Tuning Range Upper Limit | Tuning Range Lower Limit | Upper Tuning Range (PPM) | Upper Tuning Range (PPM) | Jitter (RMS/P-P) (ps) | Phase Noise 12kHz-20MHz (ps) | |

| 155.52MHz Crystal CL = 8pF, no shunt caps | ||||||

| Crystal 1 | 155.534 | 155.5052 | 90 | -96 | ||

| Crystal 2 | 155.5348 | 155.5044 | 95 | -101 | ||

| Crystal 3 | 155.5332 | 155.5036 | 84 | -106 | ||

| 155.52MHz Crystal CL = 6.5pF, no shunt caps | ||||||

| Crystal 1 | 155.5276 | 155.5 | 48 | -129 | ||

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)