PXI总线的遥测信号测试平台的设计

PXI总线的遥测信号测试平台的设计

在航天测试中,遥测系统是不可缺少的重要组成部分。它的主要作用是测量导弹、卫星、航天器及武器系统内/外部的环境参数,获取地面试验和飞行试验数据,为故障分析、指挥决策、安全控制和完善设计提供可靠信息和依据。测量综合控制器是遥测系统的核心,主要包括3部分:接收弹上CAN数据模块、测量记录各种传感器数据模块和形成PCM码流模块。测量综合控制器的可靠性是影响遥测结果的核心因素,其精度关系到导弹研制和实验过程中的实验数据可信度,其性能关系到实验的成败。在导弹的研制过程中,要历经多次试验,试验耗资巨大,所以要求测量综合控制器具有高精度、高可靠性。如何准确、客观、高效地*价测量综合控制器的性能,是测量综合控制器生产中的重要环节。测量综合控制器测试系统是集信号自动发生、自动检测、自动计量和数据分析于一体的大型应用系统,是专门针对测量综合控制器检测的测试系统。

本测试平台是测试系统中的一个分系统,主要研究如何通过PXI总线实现多种传感器信号的模拟和PCM码流的持续无丢帧存储技术。

1 系统设计

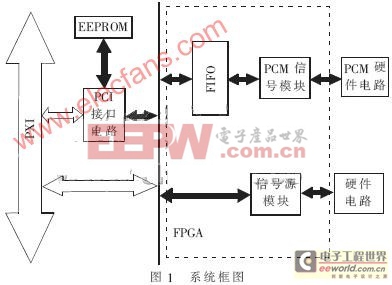

如图1所示,系统通过PXI总线与上位机进行通信,本地总线与PXI总线通过PCI接口电路连接。系统有2种工作模式:自检模式和正常工作模式。在自检模式下,系统通过硬件连接把SAR和GNSS信号接收回来,且内部模拟一个测量综合控制器上的PCM码源,再将回读后的数据在上位机上显示。

2 PXI总线及接口电路的实现

PXI是PCI在仪器领域的扩展,它将Compact-PCI规范定义的PCI总线技术发展成适用于试验、测量与数据采集场合的机械、电气和软件的规范,从而形成新的仪器体系结构。PXI将PC的高性价比优势和PCI总线向仪器领域扩展的需求完美结合起来,它通过增加用于多板同步的触发总线和参考时钟、用于精确定时的星型触发总线以及用于相邻模块间高速通信的局部总线来满足用户的测试要求[1]。

2.1 PXI总线的读写

在一个PXI总线的应用系统中,如果某设备取得了总线控制权,就称其为“主设备”;而被主设备选中进行通信的设备称为“从设备”或“目标设备”。PXI总线有2种操作模式[2]:

(1)正常模式:地址和数据交替使用AD总线。首先发送的是地址信号,接着就是数据的读写。正常模式1次传输过程需要2~3个时钟周期(地址周期+写周期;地址周期+读周期+读周期)。对1个32位宽的数据总线,最大写数据传输速度只有66 MB/s,而最大的读数据传输速度只有44 MB/s。

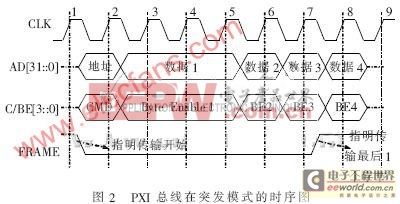

(2)突发模式:在这种模式下,主设备首先发出1个起始地址,接着是一系列隐含着地址(地址顺序增量)的数据信号。这样传输的如果是具有连续地址的内存块,对1个32位宽的数据总线,数据传输速度最高可达到133 MB/s(32位)或是266 MB/s(64位)。

本系统采用的是突发读写模式,图2为32位PXI总线在突发模式下的时序图。

在时序图的第1个时钟周期中,主控设备把地址放到AD总线上,把对目标设备的命令放到C/BE#(命令1字节选通)引脚上。C/BE#引脚上的状态标识了PXI不同种类的命令,PXI总线的操作主要体现在PXI总线命令上。总线命令出现在PXI地址期的C/BE[3::0]线上,总线命令的作用是用来规定主、从设备之间的传输类型。由图2可见,第1个数据传输需3个时钟周期,其后每个时钟完成相应的1个数据传输。

2.2 PXI总线接口实现

接口电路的功能是实现本地总线信号和PXI(PCI)总线信号之间的转换,所以接口电路的基本功能是完成读写操作控制逻辑的转换。目前PXI总线的接口方案主要有2种:使用可编程逻辑器件和使用专用总线接口器件。

(1)可编程逻辑器件实现:对于设计者来说,并不需要实现规范中的所有功能,而采用可编程逻辑器件就可以灵活地选择自己所需的功能。PXI总线对负载和传输数据的时间要求都比较苛刻,同时还需要器件内部实现配置各类寄存器,而且要实现比较复杂的应用,需要开发者对协议有深刻的了解。因此,用可编程逻辑器件方案难度较大,开发时间长,不适合小批量生产。

(2)专用PCI接口芯片+FPGA实现:专用PCI接口芯片的缺点是灵活性比较差,但其支持PCI协议,可以减少开发时间,提高效率。FPGA用来实现PXI总线所要完成的触发总线、局部总线等功能。本设计采用的就是接口芯片的方案。

PXI接口电路利用PCI9054芯片构造PCI接口。PCI9054由PCI总线接口逻辑、本地总线接口逻辑、内部逻辑和EEPROM接口逻辑组成。本地接口逻辑由可编程逻辑器件实现,包括地址/数据信号、I/O读写信号、存储器读写控制信号以及等待周期产生逻辑和总线控制逻辑等[3]。串行EEPROM采用93CS56芯片,在

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)