解决高清音频IC设计难题

iply-Accumulate, MAC)架构,是需要先进音频标准的高清音频应用的理想DSP方案。另外,CEVA-TeakLite-III还具有良好平衡的10级管线,使其内核在 65nm工艺下的运作频率仍超过550MHz(在最差条件和工艺)。CEVA-HD-Audio集成了一个带有32位寄存器文件、64位数据存储带宽、 32×32位乘法器和自动32位饱和的本地32位SIMD DSP处理器。CEVA-TeakLite-III还具有一个带有完善MAC指令集的双16×16 MAC,可实现语音/VoIP和全面的流处理位操作(bit-manipulation)功能,这对流处理十分有用。除了带有多精度点的固有32位数据处理功能之外,单周期32位MAC单元还包括用于无损编解码器的72位MAC累加,和独特的单精度与双精度FFT蝶形指令(butteRFly instruction),以及一个2/4周期内核。

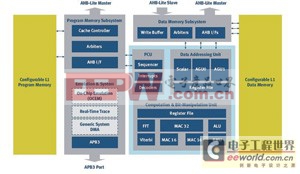

图3 CEVA TeakLite-III结构框图

CEVA-TeakLite-III架构嵌入了CEVA-Quark指令集,是全面的独立式嵌入紧凑型指令集架构(ISA)。这种独特的 ISA旨在仅利用16位指令,减小芯片的尺寸和成本,同时降低功耗,减少存储器存取次数。CEVA-Quark ISA是一套完整的指令,包括存储器存取、算术与乘法运算、逻辑、移位和流处理位操作指令以及控制操作。应用程序开发人员还可以把CEVA-Quark指令与其他更先进的CEVA-TeakLite-III指令相混合,无须切换到不同的运作模式。这种组合特性可使代码量减少4倍,周期数减少了近9倍。

利用单核实现高性能高清音频

上面提到的处理效率,显示CEVA-TeakLite-III能够利用单核DSP,轻松提供完整的高清音频支持。由于它拥有更小的存储器,所以尺寸更小,性能更高,比市场上其他竞争解决方案更为优胜。单核实现方案也意味着不论从硬件还是软件的角度来看,应用开发和集成都更为容易。

本地音频处理

CEVA-HD-Audio具有32位本地处理能力,故能为高清音频算法提供很高的精度。此外,64位的数据存储器带宽可确保 DSP不断有数据样本与系数馈入,从而实现连续处理。为应对这些挑战,CEVA-HD-Audio解决方案还备有一套完整的音频编解码器。音频编解码器算法设计使用一个普通的DMA引擎,使数据传送和算法执行能够并行进行,有助音频算法和编解码流程。另外,CEVA-HD-Audio还包含了一个带有指令缓存的存储子系统、用于数据的紧密耦合存储器和AHB/APB系统接口(包括主和从接口)。这些特性能帮助CEVA-HD-Audio用户满足复杂音频使用案例、外部存储器存取的高延时和有限的系统速度等严苛要求。它们也易于集成到基于CPU的SoC中,可以实现完整音频系统的快速产量提升。

高清音频的软件开发

一套包括C编译器、汇编器、链接器、代码库、调试器和仿真器的完整的软件开发工具也是非常重要的,因为它们能够帮助用户迅速方便地进行系统的开发和集成。一个基于GUI的开发环境也让编程人员能够轻松遵循不同的处理流程,提高编程、编译和调试流程的效率。

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)