3.2 变压器设计考虑

在SMPS设计与制作中,变压器是一个关键性元件。对于图3所示的LCD监视器回扫式SMPS电路,变压器(T1)参数的确定根据下面的设定条件:

1)AC输入电压(Vin)范围 85~265V(频率60Hz);

2)输出功率Po=Po1+Po2=2A×12V+2A×3.3V=30.6W(按30W计);

3)变换器效率η=70%。

对于变压器设计的详细步骤在这里不准备逐一介绍,只简要说明变压器设计思路及设计考虑。

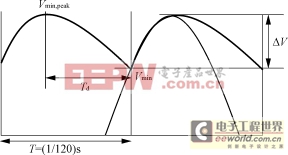

在确定变压器初级峰值电流Ipk时,首先要确定最低DC输入电压(即输入电容Cin=C103上的电压)。当SMPS在恒定输出功率上操作时,最大峰值初级电流发生在最低DC电压上。图4示出了Cin充电和放电波形。

图4 滤波电容Cin(C103)上充/放电波形

当Cin在f=120Hz下充电和放电时,在Vmin处的纹波电压ΔV最大。Cin充电峰值电压

Vmin(pk)= ×Vin(min)=

×Vin(min)= ×85V=120V。

×85V=120V。

若纹波电压(峰-峰值)按不小于线路电压的20%处理,可设ΔV=20V。于是,Cin放电谷底电压Vmin=Vmin(pk)-ΔV=120V-20V=100V。Cin放电时间td可按照式(1)计算:

td= ×

×

(1)

(1)

将已知数据代入式(1)可得:td=6.78ms。

Cin在放电期间输入能量Ein为:

Ein=Pin·td=(Po/η)×td=(30/0.7)×6.78×10-3=0.29J

根据Ein= ·Cin·

·Cin· ,可得:

,可得:

Cin= =

= =132μF

=132μF

132μF是非标准电容。在图3所示的应用电路中,Cin(C103)选用的是82μF的铝高压电解电容器。在此种情况下,Cin放电终止电压Vmin因纹波电压的增大不再是100V。假定Cin放电时的输入能量不变,根据Ein的计算公式得到的结果是:Vmin=86V。利用该结果计算Ipk时,余量较大。

最大峰值初级电流Ipk在Vmin和最大占空比Dmax下出现。由于电流控制型SMPS的Dmax应低于50%,若选取Dmax=0.45,可得:

Ipk= =

= =2.2A

=2.2A

初级方均根值电流Irms可以按式(2)计算:

Irms=Ipk· (2)

(2)

将Ipk=2.2A和Dmax=0.45代入式(2)得到

Irms=0.85A。

在大多数关于变压器初级电感量Lp的计算中,初级电流都选用Ipk。在变换器初级电感传输到次级的功率保持不变时,确定Lp时可以使用Irms,从而使Lp的计算结果有较大余量。由于FPS的固定操作频率fs=70kHz,故Lp为:

Lp= =

= =0.65mH

=0.65mH

在Ipk、Irms和Lp等参数确定之后,通常根据面积乘积公式Ap=Ae·AW≥(Lp·Ipk·Irms×104/420·K·Bmax)1.31等来确定磁芯的选取。针对本设计实例,通过简单的计算和经验,可选用EFD3030磁芯,其有效截面积Ae=1.07cm2,窗口面积(线圈骨架绕组面积)AW=2.23cm2,最大磁通密度Bmax=0.168T。

初级绕组匝数可由式(3)计算:

Np= (3)

(3)

将Lp=0.65×10-3H、Ipk=2.2A、Bmax=0.168T和Ae=1.07cm2代入式(3),可得:Np=79.6匝。可选取Np=80匝。

在最大占空因数Dmax上的初、次级绕组匝数比n为:

n= =

= (4)

(4)

式中:Vd为次级整流二极管的压降(选取0.6V);

Vo为次级DC输出电压。

设12V输出次边绕组匝数为NV1,3.3V输出绕组匝数NV2,FPS偏置绕组匝数为NVCC,根据式(4)可得:

NV1=Np× =

= =13匝

=13匝

同理可得:NV2=4匝,NVCC=24匝(Vcc按24V计)。

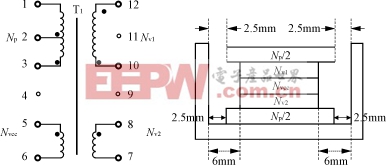

图5示出了变压器的结构,其主要参数如下:

图5 变压器结构示意图

磁芯与骨架:EFD3030;

绕组线径和匝数:

初级绕组Np(脚1→2,脚3→2):φ0.3×1,80T(40T+40T),Lp=0.65mH,最大漏感为10μH;

NV1绕组(脚12→10):φ0.3×2,13T;

NV2绕组(脚8→7):φ0.3×4,4T;

Nvcc绕组(脚5→6):φ0.2×2,24T

变压器绕组之间和外层用2层0.05mm厚的聚酯型薄膜隔离。