下一代数据包处理技术架构选择

器最终会以流水线和并行池的混合架构形态出现。

处理器核的分组对编程模式有重要影响。并行池带有相关的多线程编程模式,其中每个处理器核可运行一个或多个线程。从本质上讲就是程序获取一个数据包并对其执行一系列操作。

一旦处理完一个数据包,程序就准备好按顺序取用下一个数据包。程序员通过把数据包分配给不同的并行池来有效利用处理资源。线程之间的同步是程序员的另一个关键系统任务。

流水线模式处理数据平面应用,并将其划分为不同的处理任务(即:分类、修改、隧道处理以及状态更新)。然后,每个任务被映射到不同的处理器核,任务的执行或由架构强制完成,或交由程序员处理。由于吞吐量受限于速度最慢的部分,因此如何在各内核间有效地划分任务通常是个挑战。

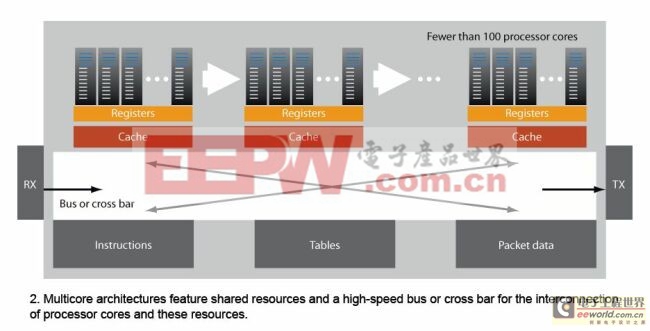

通用多核架构内的数据包通常存储在共享存储器区域(图2)。在这种情况下,程序员必须将分类和数据包修改任务分别分配给处理资源的并行池和流水线。

图2:多核架构共享资源,以及用于处理器核和资源互连的高速总线或crossbar总线。

共享数据的复杂性

在并行数据包处理过程中,多个线程可能需要访问和更新诸如状态和ARP条目等共享数据。不同的线程需要进行同步以强制互斥并实现通用共享模式。但众所周知,同步并非易事而且会对性能造成影响。

为提高性能,许多多核处理器采用硬件缓存。虽然这可以极大缩短平均存储器访问延迟,但架构会变得更难以预测。

缓存一致性协议保证了采用缓存层次结构的多核系统中数据的完整性。虽然这对于程序员是透明的,但为了调节性能,程序员需要了解缓存和一致性协议是如何运作的。另一方面,存储器一致性模型也对程序员开放。因此,程序员需要了解存储器一致性模型以编写正确的程序。

保持数据包顺序

并行数据包处理的另一个挑战是保持数据包的顺序。所有节点都应针对相关的数据包保持数据包顺序,因为上层传输协议的正常工作依赖这种顺序。了解哪些类数据包需要保持包顺序以及如何最有效地满足这一需求通常是程序员的职责。

为降低复杂度,NPU供应商通常会提供硬件支持和软件库。添加更多的数据包缓冲器可有助于确保数据包顺序,但这总是以增加延迟为代价。

降低复杂性需求

驾驭基于多核的NPU并非易事。英特尔公司的Larry Huston在第10届高性能计算机体系结构国际研讨会上发表的论文中总结道:

“理想的情况应是,程序员将应用写成一段软件,而工具会自动划分应用并将应用映射到并行资源集。这也许是个难以实现的目标,但在该方向上的任一进步都将升华开发者的开发生命。”

数据流架构正好满足这一需求。虽然Larry Huston的上述见解发表在2004年,但它在今天的效用和意义与6年前一样。

确定性数据流架构

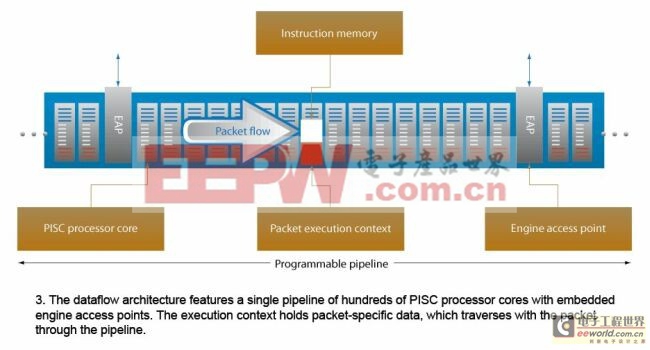

数据流架构(图3)采用了独特的方法,且具有处理器内核组成的单个流水线。该架构已被设计成完全确定性和超高效的。除执行语境外,它还包括一个数据包指令集计算机(PISC)和一个引擎接入点(EA P)。

图3:数据流架构(图3)拥有包含数百个PISC处理器内核的单个流水线,以及嵌入式引擎接入点。

PISC是专为数据包处理设计的处理器核。流水线可以包含数百个(超过400)PISC。EAP是用于分类任务的专用I/O单元。EAP统一访问存储在嵌入式或外部存储器(TCAM、SRAM、DRAM)中的存储表,并包含用于计量、计数、散列、格式化、流量管理以及表搜索的资源引擎。

执行语境是程序员可用的数据包内的具体数据。它包括数据包最初的256个字节、通用寄存器、设备寄存器和状态标志。一个执行语境唯一地对应一个数据包并使该数据包在流水线内传送。

数据包在流水线中传送就像在一个固定长度的先入先出(FIFO)设备中行进一样。在每个时钟周期,流水线内的所有数据包都前移一级以便在下一个处理器或EAP内执行。

指令总是在一个时钟周期内执行完。每条指令都能以超长指令字(VLIW)方式并行执行多达5个操作。然后,数据包继续前进到下一个PISC或EAP。

数据平面程序经编译后存储在位于处理器核内的指令存储器,从而无需在程序执行期间从共享存储器内将指令发送到处理器内核。另外,此举还显著提升了性能,降低了功耗。

编程模式反映出众所周知的顺序单处理器模式,其中,程序员可以编写顺序执行的模块以避免多个并行编程(即存储器连贯性、一致性和同步)的麻烦。当软件被编译后,程序代码会自动映射到由处理器内核构成的单一流水线。一个VLIW指令占用流水线中的一个处理器核。

这种架构和编程模式的一个显著好处是,它强制执行线速运作。每种数据包都有经确保数量的操作和分类资源。

降低复杂度,提高性能

多核架构无法保证某一水平的性能

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)