UC3855高性能功率因数校正预调节器

tZVT的固定延迟,可以实现这一目标。

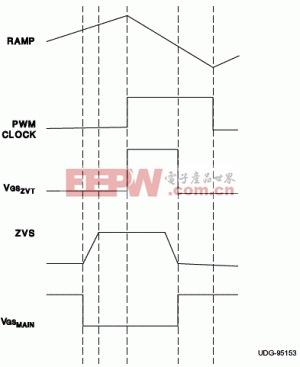

但是,这样一来在轻负载或更高线压的条件下延迟的时间会比必要延迟时间更长,从而会增加ZVT电路传导损耗以及峰值电流应力。通过感应QMAIN漏极电压何时降至为零,UC3855实现了一个可变tZVT。一旦该电压降至ZVS引脚阈值电压(2.5V)以下时,ZVT栅极驱动信号便被终止,并且主开关栅极驱动升高。图3显示了该控制波形。在振荡器开始放电时开关周期开始,ZVT栅极驱动在放电周期开始时升高。在ZVS引脚感应到零电压状态或者放电期间结束(振荡器放电时间为最大ZVT脉宽)以前,ZVT信号均处于高位。这样就使ZVT开关仅在需要的时候开启。

ZVT控制波形

2. 控制电路运行及设计

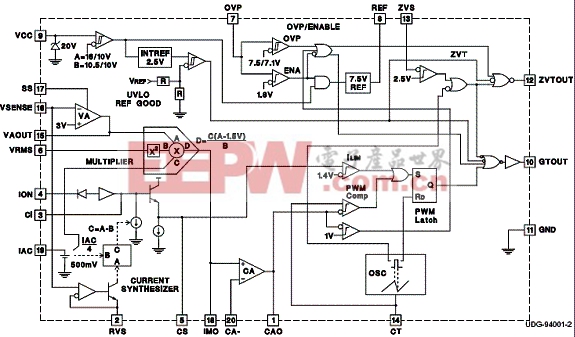

图4显示了UC3855A/B的结构图(引脚数与DIL?20封装相当)。其显示了一款集成了基本PFC电路的控制器,包括平均电流模式控制以及促进ZVT工作的驱动电路。该器件还具有简化电流传感的电流波形合成器电路,以及过压和过电流保护。在下列各章节中,该控制器件被分解成若干个功能模块,并对其进行了单独的讨论。

UC3855控制器结构图

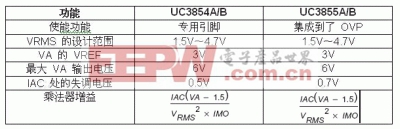

2.1 与UC3854A/B的比较

UC3855A/B的PFC部分与UC3854A/B完全一样。他们共有的几个设计参数在下面被突出显示了出来,以说明其相似性。

UC3855A/B中集成的新特性包括:ZVT控制电路、过压保护、电流合成器。

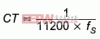

2.2 振荡器

振荡器包括一个内部电流源和散热片,因此仅需要一个外部时序电容器(CT)来设置频率。将额定充电电流设置为500μA,放电电流为8mA。放电时间大约为总时间的6%,其定义了最大ZVT时间。CT的计算可通过下式得出:

2.3 ZVT控制电路

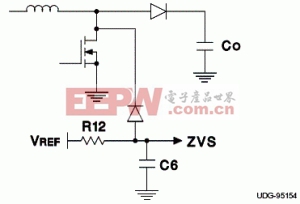

正如ZVT技术部分所述,UC3855A/B提供了控制逻辑,以确保ZVT在所有线压及负载状态下运行,并且无需使用一个固定延迟。ZVS引脚对MOSFET漏极电压进行感应,并为一个ZVT驱动比较器输入。另一个比较器输入被内部偏置至2.5V。当ZVS输入为2.5V以上(并出现PWM时钟信号)时,ZVT驱动信号可升高。下拉ZVS引脚可终止ZVT驱动信号,并开启主开关输出(最大ZVT输出信号等于振荡器放电时间)。图5显示了用于感应节点电压的网络。R12将引脚上拉至7.5V的最大值,同时C6提供滤波功能。

ZVS传感电路

RC时间常数应该足够快,以在最大占空比时达到2.5V。该漏极电压受限于将主MOSFET dv/dt变慢的节点电容,其降低了ZVS电路上的高速要求。最大ZVS引脚电压应被限制在VREF,否则ZVS电路就会变为闭锁状态,无法正确工作。

ZVS运行的另一种方法是,通过一个简单的分压器来感应漏极电压。但是,该电压仍然必须被滤波(和钳位控制),以便不会将噪声注入ZVS引脚。

如欲了解时序波形,请参考前面的图3。

3. 栅极驱动

主驱动可提供1.5APK,ZVT驱动为0.75APK。由于ZVT运行,主开关驱动阻抗要求被减少。在开启时,漏极电压为0V,因此密勒电容效应不再是一个问题;在关闭时,dv/dt受限于谐振电容器。由于ZVT MOSFET通常为至少两个小于主开关的裸片尺寸,因此一个较低的峰值电流容量就可以满足其驱动要求。

3.1 乘法器/分压器电路

UC3855A/B的乘法器部分与UC3854A/B完全一样。其集成了输入电压前馈功能(通过VRMS输入),以消除对输入电压环路增益的依赖性。正确地设置该器件,需要定义的参数只有三个(VVRMS、IIAC和RIMO)。

3.1.1 VRMS

该乘法器对线电流进行编程,从而影响线路的功耗。考滤到系统功耗限制,对VRMS引脚进行编程。参考该结构图(图4),乘法器输出方程式为:

功耗限制函数由电压环路误差放大器VEA(6V)的最大输出电压来设置。通过观察给定VEA值情况下的变化可以轻松地阐明功耗限制函数。如果该AC线压降低2倍,那么前馈电压效应(V2VRMS)则降低至四分之一。这样就将乘法器输出电流(以及随之而来的线电流)提高了2倍。因此,线路的功耗保持恒定。反之,如果负载增加且线路保持恒定,则VEA增加,从而导致更高的线电流。于是,由此可见,VEA为一个同输入功耗成正比例关系的电压。

在正常情况下,设置乘法器是用来限制低线路条件下的最大功耗,其同最大误差放大器输出电压相当。对该乘法方程式求解,以得到同最大误差放大器电压和最大乘法器电流(2倍IIAC以内)相当的前馈电压。

求出低压线路VRMS电压以后就可以定义线路至VRMS引脚的分压器。为了减少出现在乘法器输入端的二阶谐波数量(其反过来又会在输入电流中引起三阶谐波)[9],相对而言,该前馈电压必须没有纹波。该滤波会在VRMS引脚上产生一个dc电压。由于是按照其RMS值对输入电压进行定义,因此必须考虑到该RMS因数(0.9)dc[9]。例如,如果该低线压为85V,那么要求的衰减则为:

在270V高线压状态下,其相当于VVRMS=4.76V

- 新型放大器实现高性能电流检测(08-18)

- 高性能中频采样系统的设计与实现(02-13)

- ADI:高效与节能并行 共建绿色模拟市场(04-23)

- 手机USB充电和过压保护设计策略分析(12-28)

- HDTV中的模拟电路设计(09-08)

- 研扬推出全新工业级高性能嵌入式PC 适用于苛刻的工业自动化应用(12-23)