基于SoC成像芯片MT9M111和CY7C68013的视频采

CMOS图像采集系统普遍存在图像质量问题,如果没有对图像进行专门的处理,则图像质量难以保障。近些年来,随着SoC技术的快速发展,在图像采集和处理领域,出现了SoC影像传感器,它集成CMOS传感器和图形处理器功能,可以得到令人非常满意的图像质量。本文设计的视频采集系统采用了SoC成像芯片MT9M111和USB2.0接口芯片CY7C68013。

系统结构

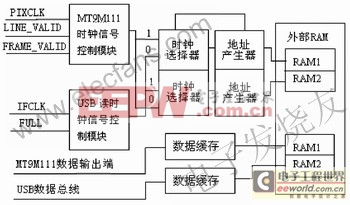

本系统的原理框图如图1所示。当图像传感器开始工作后,先将采集到的数据通过FPGA控制逻辑存储到SRAM1中,一帧图像的采集/存储过程结束后,SRAM1进入写结束状态。此时切换SRAM,SRAM2继续存储采集到的数据,同时,SRAM1处于可读状态,由FPGA里的控制逻辑控制,将SRAM1中的数据传输到USB芯片,然后传输到主机。本系统采用双SRAM结构和乒乓机制,两片存储器交替工作,使图像的采集和传输并行进行。双帧存结构不仅提高了系统的速度,而且,由于在FPGA里实现各种图像处理的算法大都需要比较大的存储空间,所以两个大容量SRAM在实现算法时可以充当外部缓存。

MT9M111

本系统采用美光公司推出的集成CMOS传感器和图形处理器的SoC产品MT9M111。MT9M111是低功耗、低成本渐进扫描CMOS图像传感器;130万像素分辨率(1280H×1024V);1/3英寸光学格式;全分辨率15fps的功耗为170mW,VGA分辨率30fps的功耗为90mW。MT9M111采用低漏电DRAM工艺,配备了美光的DigitalClarity专利技术,即使在最差的光照条件下也能提供清晰明亮的彩色图像。MT9M111具有较低的暗电流,并降低了色度/亮度干扰和瞬间噪声。MT9M111的嵌入可编程图像流处理器提供的功能包括色彩恢复和修补、自动曝光、白平衡、镜头阴影修正、增加清晰度、可编程灰度修正、黑暗电平失调修正、闪烁避免、连续调整滤光尺寸、平滑的数字变焦、快速自动曝光模式和不工作时缺陷修正等。而且,还配备了两线串行接口,USB芯片可以通过这两线串口对其进行配置。

IS61WV20488

与图像处理有关的SRAM参数主要是SRAM 的读写速度和容量。在容量方面,本系统采集图像的最大分辨率为1280×1024,数据宽度为8位,2M×8bit的SRAM可以满足存放一帧图像数据的要求。SRAM的读写速度一般为12ns、15ns、20ns或者更慢,由于SRAM的读写速度直接影响整个图像处理系统的时钟,所以,SRAM的读写速度越快越好。本系统选用了ISSI公司的IS61WV20488,芯片容量为2M×8bit。

CY7C68013

图像数据传输部分采用Cypress公司推出的专门用于USB2.0的接口芯片CY7C68013。该芯片包括带815kB 片上RAM 的增强型8051 处理器(与标准8051 系列兼容,速度提高3"5倍)、4kB FIFO 存储器和通用可编程接口I2C 总线、串行接口引擎( S IE ) 以及USB2.0 收发器。

图1 基于SoC影像传感器的视频采集系统

系统软/硬件设计

系统软/硬件设计由3部分构成:图像采集/存储模块、图像传输模块和USB驱动/主机应用程序模块。

图像采集/存储模块

该模块主要由FPGA的控制逻辑将成像芯片MT9M111采集到的图像数据实时地传送到SRAM中。在系统中采用双帧存结构,每个由一片IS61WV20488 SRAM构成,能够存放一帧1280×1024分辨率的图像数据。由于采用了乒乓机制,两片存储器之间交替工作,从而使图像的采集和传输并行进行。为确保在任何时刻只有一片SRAM可以读取采集到的图像数据,设置了一个读互斥锁,同样,只有一个SRAM可接收采集到的图像数据,因此,又设置了一个写互斥锁。需要注意的是,由于图像传感器的图像数据输出速度要比USB2.0传输速度慢,所以,当读完SRAM2的数据以后,需要等待另一片SRAM1完成写图像数据后,才可以向SRAM2写入下一帧图像数据,而SRAM1无需等待便可以直接进行读取图像数据的工作,如此循环往复,实现了并行工作,有效地提高了系统的工作效率。图2为系统控制电路的原理框图,FPGA内部各个模块均采用Verilog HDL编写。

图2 FPGA控制电路框图

图像传输模块

采集完一帧图像后,要经过USB时钟信号控制模块将外部RAM中的图像数据读入到主机。在本图像采集系统中,使用CY7C68013的Slave FIFO异步工作方式,把FIFO配置成和EP2端口相连、每个数据包1024字节、4缓冲的方式,块传输模式。这样的设置可以满足系统要求,同时也有效地利用了内部的4kB FIFO来传输采集到的图像数据,系统控制使用了FALGB信号引脚,用来报告“FIFO满”的状态,默认为低电平有效。本文采用的是自动输入方式,当FIFO中的数据满一定量时,EZ-USB-FX2就直接通过FIFO把数据传送到USB收发器,而不经过CPU的干预,这样就提高了传输速度,本系统当FIFO满1kB时开始自动发送。

USB驱动和主机应用程序模块

SoC MT9M111 CY7C68013 视频采集 相关文章:

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)