理解ATE SPI (串行外设接口)

| DIN to SCLK high setup | tDS | 10 | — | — | ns |

| DIN to SCLK high hold | tDH | 0 | — | — | ns |

| CS-bar pulse width high | tCSWH | 10 | — | — | ns |

| CS-bar high to LD-bar low setup | tCLL | 22 | — | — | ns |

| LD-bar pulse width low | tLDW | 20 | — | — | ns |

| RST-bar low pulse width | tRST | 10 | — | — | ns |

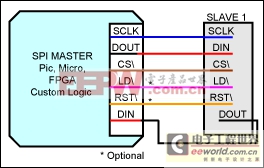

SPI接口的主/从配置

有三种方法实现主/从配置:

- 一主一从,如图4所示。

- 一主多从,采用菊花链拓扑结构,如图5所示。

该方法的优势在于:- 主器件仅需要一个片选引脚。

- 以菊花链形式将DOUT引脚连接至下一个从器件的DIN;最后一个从器件的DOUT返回至主器件DIN端口进行读取。

- 每个从器件没有独立控制信号。

- DATA字较长。

- 由于必须在触发片选信号之前更新所有从器件,所以更新速度较慢。

- 一主多从,每片从器件都有其各自的片选引脚,如图6所示。

该方法的优势在于:- 每个从器件均可独立控制。

- 工作速率较快。

- 主器件需要更多的I/O控制引脚。

- 如果DOUT不能处于高阻态,则不能回读数据。

图4. 单个主/从SPI接口

图5. 一主多从—菊花链结构,一个片选信号控制所有从器件。

图6. 一主多从—每个从器件都有独立的片选信号。

常见的SPI错误

根据数据资料确定数据是在时钟的正向上升沿还是负向下降沿移入。请注意不要混淆具有不同时钟沿要求的从器件。如果存在不同的时钟要求,请务必在软件或硬件中完成正确的转换。

根据数据资料确定是MSB在前还是LSB在前移入数据。

确保CS\在相对于时钟沿的数据字附近正确控制。

如果字长不是8位或单字节的倍数,请务必在字开头或结尾处添加零,以确保以字节的整数倍移入。有些控制器或主器件,一次只能输出1个字节。如果是这种情况,需确保不会将实际数据从从器件中移出。若要控制指定从器件,需确保从器件拥有完整数据。

请不要将多个DOUT连接在一起,除非它们具有高阻态选项。

请仔细阅读数据资料,确定已经理解、掌握从器件的使用细节。“字”可以包含数据、地址和控制位。

请注意,以菊花链连接多个器件可能导致更新速度缓慢。

SCLK信号为高速信号并送至多个位置。确保该信号经过适当缓冲以驱动多个电路,从而避免时序误差。所有驱动多个电路的信号都应该具有足够的驱动能力。

总结

从6个基本信号的角度介绍了Maxim ATE SPI串行接口的基本工作原理和时序,它们分别为:SCLK、CS\、DIN、RST\、LD\和DOUT。RST\和LD\可选。即使不同电路之间的结构会有所调整,但这6个信号的时序定义了SPI接口的外部工作特性。本文结合6个基本信号,以8位字、双缓存接口为例介绍了SPI的工作原理。该接口是Maxim ATE产品遵循的拓扑结构。查看每个器件的数据资料可以了解不同接口的差异和增强功能,但所有接口都遵循本文所述时序。充分理解本文给出的示例有助于您解读、理解Maxim的许多ATE串行接口。

*注:后缀“\” (例如:CS\、LD\、RST\)表示这些引脚为低电平有效。

- 选择最佳的电压基准源(11-29)

- 应用于手持设备的无线调制解调器电源(02-20)

- 1-Wire扩展网络标准(02-20)

- RS-485串行数据通信协议及其应用(02-20)

- 电感选择对DC-DC转换器性能的折衷(04-28)

- 提高MAX1464 ADC性能(03-11)