逻辑分析仪原理及应用

但触发电平已预设置到逻辑阈值。大部分逻辑器件都与电平相关,这些器件的时钟和控制信号通常都对边沿敏感。边沿触发使您能与器件时钟同步地捕获数据。您能告诉分析仪在时钟边沿产生(上升或下降)时捕获数据,并获取移位寄存器的所有输出。当然在这种情况下,必须延迟跟踪点,以顾及通过移位寄存器的传播延迟。

状态分析仪基础

如果您从未使用过状态分析仪,您可能认为这是一种极为复杂的仪器,需要花很多时间才能掌握使用方法。事实上,许多硬件设计师发现状态分析仪中有许多极有价值的工具。

一个逻辑电路的“状态”是数据有效时对总线或信号线的采样样本。例如,取一个简单的“D”触发器。“D”输入端的数据直到时钟正沿到来时才有效。这样,触发器的状态就是正时钟沿产生时的状态。

现在,假定我们有8个这样的触发器并联。所有8个触发器都连到同样的时钟信号上。当时钟线上产生正跳变时,所有8个触发器都要捕获各自“D”输入的数据。这样,每当时钟线上正跳变时就产生一个状态,这8条线类似于微处理器总线。如果我们把状态分析仪接到这8条线上,并告诉它在时钟线正跳变时收集数据,状态分析仪将照此执行。除非时钟跳到高电平,否则输入的任何活动将不被状态分析仪捕获。

定时分析仪由内部时钟控制采样,因此它是对被测系统作异步采样。而状态分析仪从系统得到采样时钟,因此它是对系统同步采样。状态分析仪通常用列表方式显示数据,而定时分析仪用波形图显示数据。

理解时钟

在定时分析仪中,采样是沿着单一内部时钟的方向进行,从而使事情非常简单。但微处理器系统中往往会有若干个“时钟”。假定某个时刻我们要在RAM中的一个特定地址上触发,并查看所保存的数据;再假定使用的微处理器是Zilog公司的 Z80。

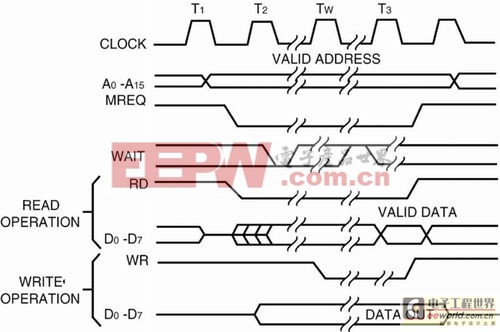

为了用状态分析仪从Z80捕获地址,我们要在MREQ线为低时进行捕获。而为了捕获数据,需要在WR线为低(写周期)或RD线为低(读周期)时让分析仪采样。某些微处理器可在同一条线上对数据和地址进行多路转换。分析仪必须能让时钟信息来自相同的信号线,而非来自不同的时钟线。

图 4 RAM 定时波形图

在读写周期期间,Z80首先把一个地址放在地址总线上。接着设定MREQ线在该地址对存储器的读或写有效。最后根据现在是读还是写对RD或WR线断言。WR线只有在总线数据有效后才被设定。这样,定时分析仪就作为多路分配器在适当的时间捕获地址,然后在同一信号线上捕获产生的数据。

触发状态分析

像定时分析仪一样,状态分析仪也提供限定所要保存数据的功能。如果我们要寻找地址总线上由高低电平构成的特定码型,可告诉分析仪在找到该模式时开始保存,直到分析仪的存储器完全装满。

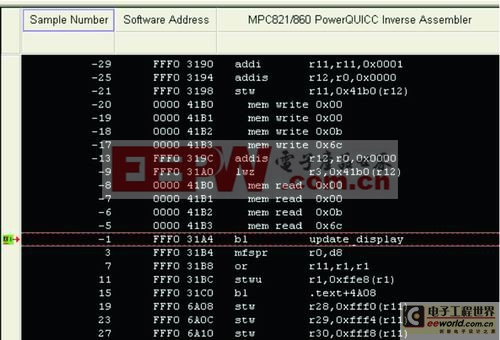

这些信息可以用十六进制或二进制格式显示。但在解码至汇编码时,十六进制可能更为方便。在使用处理器时,应把这些特定的十六进制字符与处理器指令相比较。大多数分析仪制造商设计了称为反汇编器的软件包,这些软件包把十六进制代码翻译成易于阅读的汇编码。

图 5 把十六进制码翻译成汇编码

序列级和选择性保存

状态分析仪具有帮助触发和存储的“序列级”数据。序列级使您能比单一触发点更精确地限定要保存的数据。也就是说可使用更精确的数据窗,而不必存储不需要的信息。

选择性的保存意味着可只保存较大整体中的一部分。例如,假定我们有一个计算给定数平方的汇编例程。如果该例程不能正确计算平方,我们就告诉状态分析仪捕获这一例程。具体做法是先让状态分析仪寻找该例程的起点。当它找到起始地址时,我们再告诉它寻找终止地址,并保存两者之间的所有信息。当发现例程结束时,我们告诉分析仪停止状态保存。

探测解决方案

为进行调试,向数字系统施加的物理连接必须方便可靠,对被调试的目标系统只有最小的侵扰,这样才能使逻辑分析仪得到精确的数据。

普通的探测解决方案是每条电缆有 16 个通道的无源探头。每个通道的两端用100kΩ并联8pF 端接。您可将这种无源探头与示波器探头的电气性能作一比较。无源探测系统除了更小的尺寸和更高的可靠性外,还能把探头端接在与目标系统的连接点上。这就避免了从大的有源探头接口夹到被测电路之间大量引线所产生的附加杂散电容。因此您的被测电路就只“看到”8pF的负载电容,而不再是前述探测系统的16pF。

图6 分析探头

把状态分析仪接到微处理器系统需要进行机械连接和时钟选择。某些微处理器可能需要外部电路对一些信号进行解码,才能得到用于状态分析仪的时钟。分析探头不仅能提供与目标系统快速、可靠和正确的机械连接,而且能提供必要的电气适配能力,如为正确捕获系统运

- 基于非线性效应的光学逻辑门研究(08-06)

- 过程控制和PLC设计指南(06-28)

- 3V DAC在±10V中的应用(06-21)

- 大机组MFT硬跳闸回路设计方案(07-20)

- 基于MSI的N进制计数器设计方法研究(02-01)

- 不外接电阻的双输入采样保持放大器(03-11)