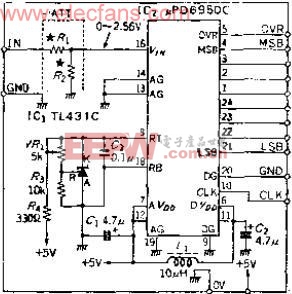

快捷式8位高速A-D转换器电路及原理介绍

电路的功能

高速8位A-D转换器用来处理视频宽带信号或用于高速电路中。

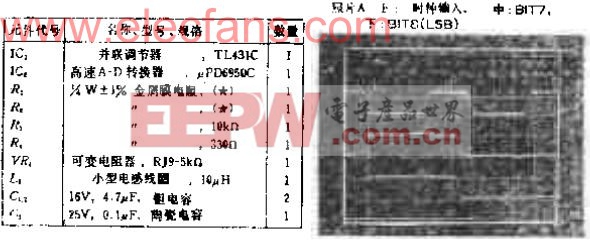

UPD6950C是由C-MOS电路组成的快速ADC,转换速率达15MSFS,模拟信号读入时大约为30NS,并由下一个间时钟脉冲锁存数据。工作电源为单极+5V,消耗功率400MW属于快速、低功耗器件。

电路工作原理

IC内部为快捷式,由256个电压比较器、产生基准电压的电阻分压电路、锁存256-8位的编码器或8位数据锁存器组成。

A-D转换原理非常简单,256个比较器接通几个进行转换,其个数可由译码器译成8位数字数据。

基准电压加在电阻分压电路的两端,其电压范围为2.5V~VDD-1(V),内部电阻为1.5K,所以分压电阻有1.6~2.6MA的电流流过。

如果基准电压为2.56V,1LSB的平均电压为10MV,这从直觉上是很容易理解的。本电路使用了并联调节器,基准电压可调范围约为:2.5~3.75V。

由于TL431C的内部基准约为2.5V,基准电压不能降到2.5V以下,所以可进行A-D转换的输入电压范围为0V~基准电压。在测量中,有时要求输入0~5.0~10V的电压,所以在输入端加了衰减器,0~10V时用1/3.9的分压器,即R1=2.9R2。

要使本电路工作,须加外部时钟脉冲,最高时钟频率可达15MHZ。应注意数据的时序问题:第一个时钟周期用于A-D转换,第二个时钟周期用来在8位数据寄存器上寄存转换好的数据,再延迟一个时钟周期才能获得转换数据。这种时序适用于进行连续,如用触发式转换、则要两个时钟脉冲信号。

照片A示出了用10MHZ的时钟频率进行连续转换的最低有效位和最高有效位的输出。时钟脉冲位置对应的数据是前一个时钟周期转换和数据,所以10NS+33NA才是真正的转换时间,不过转换时间通常仍取33NA。

当输入电压于基准电压时,“OVER”端为“H”电平,数据位也均被置为“H”电平。数据位也均被置为“H”电平。

组装注意事项

在高压电路中,组装得如何将直接影响电路的性能,为防止输入信号线与逻辑线路耦合,线路板地线布置范围要大,模拟部分与数字部分要分开。在电路图中,A-D转换器左侧为模拟部分,右侧为数字部分,组装电路时应注意。本电路采用5V单极电源,,因此要十分注意模拟、数字的接地处。

- 高精度ADC布线技术介绍(06-13)

- 快捷式8位高速A-D转换器(05-19)

- 连续时间Sigma-Delta模/数转换器(上)(05-05)

- 8位MCU如何升级至32位MCU (10-07)

- 低价32位MCU大军压境,8位ASIC MCU看涨(12-14)

- 8位MCU(微控制器)设计趋势:CISC向RISC低头(12-11)