采用Verilog的数字跑表设计

数字跑表的显示可以通过编写数码管显示程序来实现,本实例只给出数字跑表的实现过程。读者还可以通过增加小时的计时功能,实现完整的跑表功能。

实例目标

本实例主要实现了计数及进位的设计,通过几个always模块的设计实现一个特定用途的模块——数字跑表。通过本实例,读者应达到下面的一些实例目标。

? 初步掌握Verilog语言的设计方法。

? 完成一个数字跑表的设计。

原理简介

本数字跑表首先要从最低位的百分秒计数器开始,按照系统时钟进行计数。计数至100后向秒计数器进位,秒计数器以百分秒计数器的进位位为时钟进行计数。计数至60后向分计数器进位,分计数器以秒计数器的进位位为时钟进行计数,读者可以自行增加小时计数器。

数字跑表巧妙地运用进位位作为计数时钟来减少计数的位数。如果统一使用系统时钟作为计数时钟,那秒计数器将是一个6000进制的计数器,而分计数器将是一个3600000进制的计数器。这样将极大的浪费FPGA的逻辑资源。而使用进位位作为计数时钟,只需要一个100进制的计数器和两个60进制的计数器。

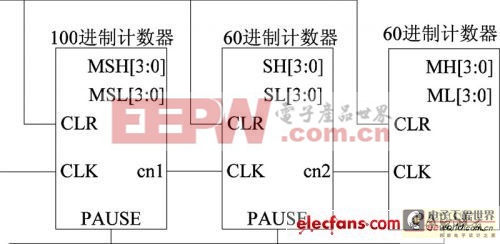

如图是本实例的数字跑表模块图。

在实际的设计中,为了使计数器更加简单,计数器使用高低位两个计数器实现。100进制计数器分别是高位10进制计数器,低位10进制计数器;60进制计数分别是高位6进制计数器,低位10进制计数器。这样整个数字跑表使用6个计数器实现。

同时由于10进制计数器重复使用了5次,可以使用独立的模块实现10进制计数器,这样就可以通过模块复用来节省整个模块使用的资源。

数字跑表提供了清零位CLR和暂停位PAUSE,百分秒的时钟信号可以通过系统时钟分频提供。分频至1/100s,即可实现真实的时间计数。详细的时钟分频设计读者可参考相关的资料实现,在本实例中不再提供。

- PCM串行数据流同步时钟提取设计(02-25)

- 一种数模混合SoC设计协同仿真的验证方法(04-09)

- 基于FPGA的∑-△D/A转换器的设计与实现(04-23)

- 基于ISP芯片的可编程数字移相器设计(06-23)

- 一种锁定相位编程可调全数字锁相环设计(06-24)

- 基于Virtuoso平台的单片射频收发系统电路仿真与版图设计(07-18)