高速数模转换器AD9779/AD9788的应用

AD9779是ADI公司的一款产品,是双通道、宽动态范围数模转换器(DAC),提供1 GS/s采样速率,允许高至奈奎斯特频率的多载波生成[1]。AD9788提供800 MS/s的采样速率,其性能和应用方式与AD9779非常相似[2]。AD9779和AD9788虽然不是一个系列,但芯片管脚是兼容的,在硬件电路的设计上并没有区别,两者均使用标准的SPI接口来驱动,因此软件实现上也可以采用统一的驱动方式。但在寄存器的配置上,两者存在差异,这在后面会具体介绍。为了描述方便,如不特殊说明,下文中使用AD97××来统一表示AD9779和AD9788。

1 AD97××的SPI规范

AD97××采用标准的4线SPI接口进行通信,当然也可以配置成3线SPI接口。

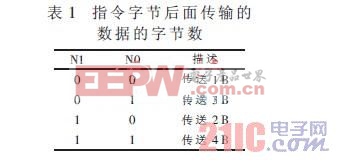

一个寄存器的读写周期(或叫传输周期)包括两部分:指令部分和数据部分。指令部分是一个8 bit的字节,对应于8个时钟的上升沿,用来控制读写以及随后需要读写的数据字节数。D7为读/写标志位(其中读为高,写为低),D6和D5是用来配置指令字节后面需要传输的数据的字节数,通常配置如表1所示(N1和N0对应指令字节中的D6和D5),D4~D0是AD97××寄存器的地址。

需要特别说明的是,对于AD9788,指令字节的D6和D5两个位被屏蔽了,因此这两位不需要配置,指令字节后面需要传输的数据的字节数是由寄存器本身来决定的。例如对于一个32 bit的寄存器,指令字节后面需要传输4 B的数据。

2 AD97××的驱动方式

AD97××主要通过SPI驱动,实现寄存器的读写和功能的配置。

将AD97××的代码分为两部分设计,一部分是底层的SPI接口驱动,完成SPI接口的初始化、读写以及设备封装等功能;另一部分是AD97××本身的驱动,主要通过SPI封装的读写接口实现对AD97××芯片的控制。

3 AD97××的配置说明

3.1 寄存器长度不固定的问题

AD9779的寄存器长度是固定的8 bit,但AD9788的寄存器长度是不固定的,有8 bit、16 bit、32 bit,还有24 bit。datasheet中规定一个寄存器的读写传输周期由寄存器本身决定,包括一个指令字节和实际传输的数据字节数,例如,0x00寄存器传输周期为2 B,0x01寄存器传输周期为3 B。因此对于AD9788,不能用统一的读写传输周期,例如5 B(8 bit指令+32 bit数据),而是需要对不同长度的寄存器分开处理,这就意味着需要模拟四种不同的SPI时序。

3.2 个别寄存器回读时应注意

在写寄存器操作时,一般需要回读一下来判断写的值是否正确。回读时要注意以下两种情况,否则会判断错误:

(1)有的寄存器个别位是只读的,与写进去的值没有关系,回读时最好屏蔽掉相关位。例如AD9788的0x04寄存器的高三位(23 bit~21 bit)为只读;AD9779也有类似的寄存器,例如0x00寄存器低三位(2 bit~0 bit)也是只读;

(2)寄存器在配置完后就发生了变化,这种寄存器一般是指示寄存器,例如AD9788的0x09寄存器,有一个锁定指示位,配置完后,若PLL锁定,这一位会改变,读出的值和写的值就会不一样。

3.3 AD97×× PLL的配置

PLL的配置是AD97××配置中的一个重点,AD9779与AD9788的PLL结构是相同的,不同的是AD9788比AD9779多了一个NCO,用于频点搬移。本节以AD9788为例讲述PLL相关寄存器的配置。

在AD9788的数据手册中,共有15个配置寄存器,其中与PLL相关的寄存器主要有0x01、0x04两个寄存器。不过由于要进行频点搬移,所以还要对0x0a寄存器按照系统需要进行配置。这样一来,只需关注0x01、0x04和0x0a这三个配置寄存器就可以了。

3.3.1 DCTL寄存器

DCTL寄存器(DIGITAL CONTROL REGISTER)参数为:地址:0x01h;宽度:2 B;默认值:0x3100;定义值:0x31c0。在此寄存器中,主要关注bit[7:6]的设置,如果系统要求DAC实现8倍内插,就要配置bit[7:6]=11,其他位按默认值即可。

3.3.2 PLLCTL寄存器

PLLCTL寄存器(PLL CONTROL REGISTER)参数为:地址:0x04h;宽度:3 B;默认值:0x3837cf;定义值:0x2fb387。

在对PLL的CTL寄存器进行设置时,主要关心bit[15:

11]和bit[7:2]值的设置,bit[15]默认是PLL无效,所以要配置bit[15]=1;bit[14:13]和bit[12:11]要根据具体系统需求配置,本例中配置为bit[14:13]=01,bit[12:11]=10,bit[7:2]的值通过式(1)计算并查表2后决定。

fvco=frefclk×N1×N2 (1)

经过查表2可知,bit[7:2]可以取100001或者100000,为了使1 474.56 MHz尽量接近于PLL Lock选择范围的中间位置,所以选用bit[7:2]=100001。对于其他位,按器件手册上推荐的最佳

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 利用GM6801实现智能快速充电器设计(11-20)

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 12位串行A/D转换器的原理及应用开发(10-09)