将高性能RF信号链集成至更小空间

需前端镜像滤波器以及尺寸相对较大、损耗较高的IF SAW滤波器。这种方法具有空间优势,但对频率非常敏感。由于无需担心IF和频率规划,因此接收机的频率范围仅受PLL、IQ解调器和前端LNA的工作范围的限制。宽带IQ解调器和PLL的选择范围广,所以这种方法非常适合可再配置的无线电应用。

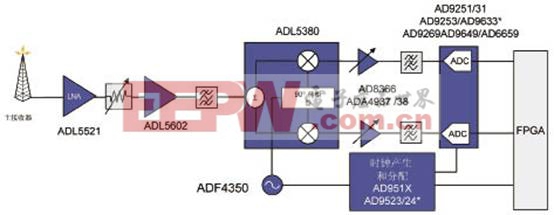

图5 直接变频接收架构

采用直接变频具有潜在的空间优势。在分集中频采样接收机和分集零中频接收机的布局中值得注意的是,空间使用率与外部无源组件密切相关,与其他方面的关系则不大。中频采样接收机具有一个长而窄的结构,这是因为它需要两个滤波器级,一个是SAW滤波器,另一个是ADC之前的抗混叠滤波器。因此,零中频接收机只需一个滤波器,而中频采样接收机则需要两个滤波器。

从性能和功耗两方面比较这两种架构,在ADIsimRF中,对一个典型中频采样接收机所做的信号链分析,在此增益设置下,输入IP3和噪声系数分别为27.8 dBm和4.7 dB,功耗为2.2 W。

如果在ADIsimRF中仿真一个等效的零中频接收机,输入IP3大致相同,但噪声系数为2.1 dB,相对较低。这主要是因为零中频架构中不存在高损耗SAW滤波器。功耗为3.17 W,相对较高。可以把这归因于需要两个ADC和两个基带放大器来驱动它,相比之下,中频采样接收机中只需要一个。虽然中频采样ADC的功耗通常高于基带采样ADC,但由于需要两个基带ADC和两个ADC驱动器,因此功耗优势不复存在。

然而,这里有一个因素未被考虑,那就是中频采样接收机所需的数字下变频电路的功耗。这一因素可能会使两种方法的功耗大致相当。

若试图去除中频采样接收机中的某些可集成器件。这里,有源混频器集成了小数N分频PLL和窄带VCO。除了驱动混频器以外,LO还能供外部使用。也可以由外部LO源驱动。

零中频接收机无需IF SAW滤波器来抑制不良的带内和带外信号。在零中频接收机中,消除所有不良信号的任务落在ADC之前的抗混叠滤波器肩上。ADRF6561这款器件提供50dB的可变增益,以及以1dB步进变化的1MHz~30MHz可编程滤波器带宽,所有这些特性都在一个5mm×5mm LFCSP封装内实现。

发射信号链的演变

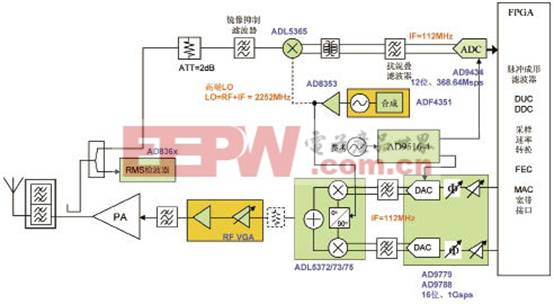

零中频发射机的功能框图如图6所示。对于500MHz~6GHz范围的无线电频率,使用IQ调制器直接跳变到RF已非常流行。发射端采用零中频比接收端更普遍,接收端仍以使用IQ解调器的中频采样或中频到基带转换为主。

图6 零中频发射机的功能框图

本例中,发射机还包括一个回送电路,它监控功率放大器的失真,并向基带中运行的数字预失真算法提供反馈。这种配置不是真正的零中频,而是所谓的复中频,DAC输出为112 MHz。因此,可以使用单个LO来驱动IQ调制器和回送混频器。 如果使用集成PLL和VCO的IQ调制器,可以再进一步,除了用于IQ调制器以外,还可以从芯片中引出LO信号以驱动DPD混频器。

总结

首先,针对存在专用芯片组的常用无线标准,设计分立电路毫无疑问是不可取的。采用分立器件进行设计时,我们拥有相当大的灵活性,但要付出功耗更高的代价。使用直接变频发射机和接收机可以节省空间,但与传统收发器相比,功耗节省可能不大。

双通道器件确实可以节省空间,但须确保通道间泄漏在合理范围内。如果一个集成VCO的PLL可提供合理水平的相位噪声,那么这将是分立RF电路设计中最能节省空间的地方之一。

问答选编

问:ADI公司的RF信号链解决方案具体包括哪些内容?

答:包括框架构建、各组件选型、链路参数设计等。

问: RF信号链与以往的产品差别是什么呢?

答:考虑无线收发器的设计方法时,我们必须尽早决定是否以分立方式构建电路。 要实现蓝牙、Zigbee或GPS等常用无线电标准,采用分立方案意义不大。 同样的道理,高度集成的芯片组除了它的本来的应用外,几乎没有其他用处。一般从空间角度考虑,高度集成的芯片组较佳,但往往灵活性不足,而且性能低于采用分立器件实现的电路。这自然引出下面的问题:是否有一个两全其美的解决方案?也就是说,它既有一定的集成度,可以节省空间,同时能为设计人员提供适当的灵活性。

问:抗干扰问题怎么解决?在集成度较高的方案中,集成VCO的好处是什么?

答:对于集成度较高的方案而言,很多接口都是内部实现的。可以省去了外部接口电路,自然外围电路就少了很多,集成VCO,可以让客户的设计省去了外围的的VCO电路等。

问:在小芯片上实现高集成是否会导致各单元电路间的相互干扰?

答:电路干扰是肯定存在的,但是ADI的完整的芯片集成设计技术可以更好的降低干扰,使集成IC的性能可以满足系统性能的指标要求。

问:为了节约成本和降低体积,兼容各项3G标准,有一种新

- 关注能效性能,提高性能,节约能源(06-24)

- 一般性柔性线路板的性能与参数(06-30)

- 新型放大器实现高性能电流检测(08-18)

- 简化Li+电池充电器CC-CV充电测试(01-16)

- 一种高效反激式开关电源的设计与性能测试(10-05)

- 高性能中频采样系统的设计与实现(02-13)