堵住电流泄漏:摩尔定律在晶体管发展中继续有效

受到物理限制,电子工程师必须构想出更加精巧的晶体管

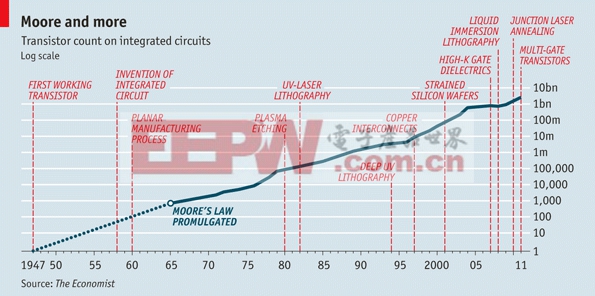

1965年,戈登•摩尔预言,在一定大小的芯片上所能容纳的晶体管的数量每两年就会增加一倍,这就是所谓的摩尔定律。多年来这个定律一直在发挥作用。第一个集成电路(由德州仪器的杰克•基尔比发明,见图)还只是一个笨拙不堪的大家伙,而现在晶体管已需用纳米(1米的十亿分之一)来计量。人们以摩尔定律的发展速度创造了快速而智能化的计算机,图案漂亮并将世界联接在了一起。从摩尔博士创立这个定律的时候起,人类就进入了一个不可思议的信息技术时代。本来一个不经意的发现竟有如此强大的生命力。

其实它并不是一条真正的定律,而只是一种现象,一种对技术发展漫漫征程的描述,发展的每一步都包含着具体的技术变革(见图表)。技术发展势不可挡,已成预言般的信条。晶体管的每一次“缩身”,都是朝着它们的最小尺寸迈进了一步。如果按此定律继续发展,20年之内,晶体管将会与几个单晶硅原子大小相当。

说得更精确一点,晶体管已经很小很小,在这样大小的空间中每个原子都变得举足轻重。原子太少它们之间的绝缘性消失,或者因“量子隧穿”现象(一种电子自然消失、并在他处重现的现象)将电流泄漏到本不该流向的地方。不适当种类的原子太多效果同样不妙,这会影响晶体管的导电性。因此工程人员正在努力重新设计晶体管。这样看来,摩尔的预言在未来的一段时间里还将继续有效。

原子核母板

晶体管实际上是一个电子控制的转换器,它由4部分组成:源极(电流从该极流入),漏极(电流从这里流出),(连接源极和漏极的)沟道以及栅极(通过电压的变化控制通道的开关)。在传统的晶体管中,这些组件都分布在同一个平面上。要防止漏电,一种思路就是把晶体管改为三维设计。

制造一个从母体芯片上伸出来的晶体管可以使许多组成原子的布置更加有效,特别是那些构成了通道和栅极的原子。将通道外伸、三面围以栅极原子,这样就能够增加栅极的表面积,更好地控制通道,并减少泄漏。在导通状态下,晶体管栅极的功能越是优良,通过的电流就越大。

五月份,美国著名的芯片巨头英特尔(摩尔博士也是该公司创建人之一)宣布一项计划,对这种营销时冠以“三栅极”的技术设备进行商业性开发。公司预计,新晶体管将于今年晚些时候面世,这种晶体管比现有的晶体管省电一半,特别适合于笔记本电脑使用,毕竟,电池寿命是笔记本电脑的一大卖点。

全面改用三维模式,这在一个成熟的行业内很难推广,毕竟他们的二维模式已经成熟。包括美国公司Globalfoundries、英国公司ARM在内的绝缘硅联合会,试图把提高平板晶体管作为他们的一个替代方案,该联合会的技术是把在一个纯硅片薄层内部制作晶体管,这层纯硅下面是一个绝缘层,再下面是一个标准晶片,这个标准晶片被用作基底,用来安放晶体管。这种方法要把晶体管的沟道做得足够薄,使栅极产生的电磁场能够透过整个沟道,提高栅极所能发挥的最大控制力。但这种方法迫使绝缘硅联合会必须面对晶体管尺寸不断缩小而产生的第二个问题:偏离正常位置的原子要么太多,要么太少。

为了改善电子性能,制造晶体管所用的硅材料中常需掺入其他元素。最新的晶体管尺寸非常小,在其沟道中掺杂只要往硅中注入少量杂质原子,如果这个量掌握得不好,晶体管的正常运行就会受到影响。但制造过程中的偏差使得这种要求很难达到。绝缘硅联合会希望使用的超薄沟道掺入杂质的工艺极其困难,因此,他们决定不向硅中掺入杂质,而用纯净硅来制造晶体管的沟道。但这要求硅层厚度不能超过5纳米。而且在整个晶片上这个厚度几乎要保持一致,英特尔公司(应当承认,它并不是一个心平气和的旁观者)认为,如此精准的标准,肯定会增加晶体管的制造成本。

SuVolta是硅谷的一家小公司,他们提出了另一种方法。他们计划制造的平板晶体管通道也不掺入杂质。但这家公司打算使用价格低廉的传统硅晶片,而不必改变晶片的成分,不必制造绝缘硅联合会要求的超薄沟道,他们的过人之处在于,在沟道的下面增加一个栅极。两个栅极共同作用就能够控制没有添加杂质并且厚度不够小的沟道。就这样,功能更好而能耗更低的晶体管就产生了,该公司表示,它的能耗减少到只有传统类型的晶体管能耗的一半,而性能上并没有损失。SuVolta此举激起了日本电子巨头富士通的极大兴趣,目前他们已拥有这项技术的生产许可。

还有多少发展空间

所有这些方法都意味着摩尔定律至少在未来几年内还会继续发挥作用。数百位专家每年都要

- 利用工程加工基板实现晶体管微缩化之途径(08-20)

- 超越摩尔定律的新技术MEMS(11-29)

- 智能手机电池六大注意事项(06-06)

- 未来处理器基石! 3D晶体管让摩尔定律延续(04-13)

- 利用单晶体管构建智能的电池充电器电路(03-05)

- 采用双极型晶体管的直流250mV转换器(07-28)