基于TMS320VC5509与AD7322的数据采集系统的设计

AD7322的功能结构如图2所示。其中是片选信号,低有效。这个脚的输入电平有两个功能,一个是AD7322转换初始化的标识,一个是串行数据搬移帧的标识。VIN0、VIN1是模拟输入通道0和模拟输入通道1,模拟输入通道的转换是通过控制寄存器的通道地址位ADD0来进行选择。如前文所述,输人通道可以接收±10 V,±5 V,±2.5 V的双极性电压输入,也可以接收0~+10 V范围的单极性电压输入。VSS是为模拟输入部件提供的负极性电压,VDD是为模拟输入部件提供的正极性电压。VCC是提供给AD7322片上的ADC的核心电压2.7~5.25 V,该端去耦到模拟地。VDRIVE提供输入的逻辑电压,这个电压决定了片上接口工作的电压范围,该引脚去耦到数字地,而且该电压可能与VCC引脚上的电压不相同,但是不能超过VCC电压的0.3V。REFIN/OUT是输入输出参考电压,AD7322包含一个2.5 V的内部参考电压,当选用内部参考电压时,在这个引脚上要放置一个680nF的电容,当使用外部参考电压时,内部参考电压失效。DIN是数据输入引脚,该引脚上的数据是写到片上寄存器中的数据,并在SCLK时钟的下降沿打入到寄存器中。DOUT是串行数据输出引脚,转换的输出数据以一个串行数据流形式输出在该引脚上,并且这些数据位在输入SCLK的下降沿被输出,经过16个SCLK后才可以访问这些数据。这个数据流包含2个前导0,1个通道说明位,1个符号位,12个转换数据位。输出的数据的第一位以高字节开始。SCLK是串行时钟输入,一个串行时钟输入需要提供给SCLK来用做从AD7322访问数据的时钟。这个时钟也用做转换过程的时钟源。

1.4 DSP模块

DSP芯片采用Ti公司的TMS320VC5509,它是一种高性能、低功耗、定点数字信号处理器,其主要特点如下:

1)最高主频能够达到144MHz,指令周期6.94ns。

2)CPU的内部总线结构包括一条程序总线,三条数据读总线,两条数据写总线及用于外设和DMA控制器的总线。这些总线使得C5509能在一个时钟内完成三次数据读操作和两次数据写操作。5509还拥有两个乘法累加器(MAC),每个累加器都能够在一个周期内执行一个17bitx17bit的乘法运算。

3)128 kx16 Bit的片上ROM,包括64 k Bytes的DARAM(8块,每块4 kx16 Bit),192K Bytes的SARAM(24块,每块4 kxl6 Bit)。

4)64 k Bytes的一等待片上ROM(32 k×16 Bit)。

5)最大可寻址8 Mxl6 Bit的外部存储空间。16位的外部存储器扩展接口可实现与异步存储器件(SRAM、EPROM)和同步存储器件(SDRAM)的无缝连接。

6)片上外设包含:

2个20 Bit的定时器;

1个看门狗定时器;

1个六通道的直接存储器访问控制器(DMA);

1个主机接口(HPI);

3个多通道缓冲串行口(Mcbsp);

2个多媒体卡(MMC)或安全数字存储卡(SD Card);

1个可编程的数字锁相环时钟发生器;

7个通用输入输出口(GPIO)和1个外部标志输出引脚(XF);

1个通用串行USB接口(12 Mbps);

1个内部集成电路模块(I2C);

1个实时时钟(RTC);

1个两通道的10Bit的逐次逼近式模数转换器(ADC)。

7)JTAG仿真接口,符合IEEE1941.1标准(JTAG)边界扫描逻辑。

1.5 A/D转换器和CCD以及DSP的接口设计

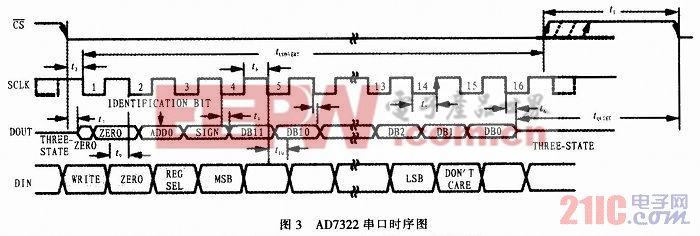

AD7322在数据转换过程中,采用SCLK引脚上的串行时钟用做转换时钟和控制从ADC中搬移数据的时钟。的下降沿使得采样与保持电路进入保持状态并使总线为三态输出,然后模拟输入信号被采样。一旦转换开始,总共需要16个SCLK时钟周期才能完成。在第14个SCLK的上升沿,采样与保持电路回到跟踪模式,在第16个SCLK的下降沿DOUT脚回到三态输出状态。如果经过16个SCLK时钟周期,的上升沿到来,则转换被中止,且DOUT脚回到三态输出状态。根据 在什么时候信号的电平变高,被选择的相应寄存器才有可能被更新。具体的串口时序如图3所示。

在什么时候信号的电平变高,被选择的相应寄存器才有可能被更新。具体的串口时序如图3所示。

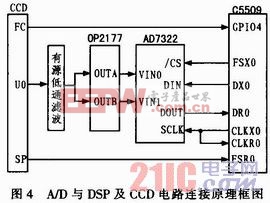

AD7322与CCD、DSP连接的原理框图如图4所示。

具体的连接方法是将CCD的行同步信号FC接入DSP的通用输入输出引脚GPI04脚。将CCD的像元同步信号SP接入DSP的McBSP帧同步输入脚FSR,控制每一个像元的采样与转换。将DSP的帧同步输出脚FSX脚接入AD7322的CS脚作为A/D芯片的选通信号。将DSP的McBSP的时钟输出脚CLKX和时钟输入脚CLKR接至AD7322的串行时钟SCLK,保证A/D转换器和McBSP工作在同一时钟下。将CCD的模拟输出信号U0经一个二阶有源低通滤波电路滤波并经过一个双运放OP2177进行驱动后的两个输出接入AD7322的两个模拟输入端VIN0和VIN1。将DSP的数据输出引脚DX接入AD73 22的DIN引脚,作为对ADC的控制信号。将AD7322的输出引脚D0与McBSP的数据输入引脚DR相连。另外,本系统中的AD7322的参考电压用的是ADC内部的参考电压,所以需要在REFIN

- 基于四路同步水声信号记录仪设计方案(10-06)

- 基于TMS32OVC5509 DSP的FIR数字滤波器的实现(05-19)

- 基于DSP的液晶显示若干问题的探讨(06-02)

- 基于DSP的全桥移相控制感应加热电源研究(01-04)

- 一种提高TMS320F2812 ADC精度的方法(08-23)

- 有源电力滤波器中的谐波检测电路设计(01-14)