一种新型高速CMOS全差分运算放大器设计

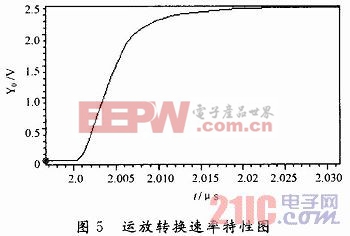

如图1所示,M11,M18构成共模反馈电路。由于本文设计的运放的直流增益较高,若采用传统的电阻采样,电阻值很小,不但占据很大的面积,还会严重的降低直流增益。因此本文采用共源放大器差分输入对管对共模电平取样的共模反馈电路。 共模抑制比定义为差分增益和共模增益的比值,它反映了一个放大器对共模信号和共模噪声的抑制能力。利用2个运放分别在输入端接差模响应激励和共模响应激励,经Spectre仿真结果测得结果如图4所示,差模增益为71.1 dB,共模增益为-46.3 dB,即可得共模抑制比为117.4 dB。 在运放输入端加入阶跃响应激励,在2μs时刻输入2.5 V的阶跃信号,仿真结果如图5所示,测得运放转换速率可达368.7 V/μs,建立时问为12.4 ns。

同时使用了一种新的连接方法,即将控制电压连接到PMOS共源共栅管M7,M8的栅极,而不是如传统方法那样接到负载管M3,M4,因此也将一般的PMOS电流镜改为NMOS电流镜。为了使输出信号摆幅最大,共模参考电压值通常为电压源的一半。

下面分析此种接法的优势。传统的接法是将控制电压接到M9和M10的栅极,这样电路的直流增益有式(1)变为:

由于在设计中I1≈I9,而考虑到输出摆幅的影响,Veff1≈3Veff9因此3gm1≈gm9。有此看来,式(6)的增益比式(1)增大了三倍。整个电路也必然的出现不稳定性,在共模反馈回路中主运放的相位与频率的关系就发生变换,因此各器件参数又需要重新调制。而将控制电压接到M7-M8的栅极,则闭环增益变为:

而Gm7=gm7/(1+gm7ro9),约小于gm1。这样CMFB环路增益稍低于主运放增益,而相位裕度基本不变,性能稳定。

4 仿真结果与分析

使用SMIC0.25μmCMOS标准工艺模型,在Cadence的spectre工具进行仿真。运放在在2.5 V单电源和驱动0.5 pF负载时,开环增益为71.1 dB,单位增益带宽为303 MHz,相位裕度为52°,仿真结果如图3所示。

5 结语

5 结语

基于流水线ADC系统应用的要求,设计了一种新型的高速运算放大器。该运放采用全差分折叠式共源共栅结构为主运放和共源放大器差分输入对管对共模电平取样的连续时间共模反馈电路。同时使用了一种新的连接方法,在保证高速的同时提高了运放的稳定性。经仿真测得在2.5 V单电源并接0.5 pF负载电容的条件下,运放直流增益可达71.1 dB,单位增益带宽303 MHz,相位欲度52°,共模抑制比达117.4 dB,转换速率高达368.7 V/μs,建立时间12.4 ns。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)