新一代SoC整合音频编解码器的挑战与设计实现

在当今的多媒体系统芯片中整合进经过硅验证并针对特定音频功能优化过的音频IP,有利于降低功耗、减少体积和缩减成本。但随着下一代设计走向 28nm工艺技术,也随之会出现新的挑战。音频编解码器中的音频设计包括了很多模拟电路,它不会随着工艺技术的发展而与时俱“小”,因此并不遵循传统的摩 尔定律。

28nm工艺技术增加了晶圆成本,系统架构师和SoC设计师必须要考虑这对将音频编解码器整合进SoC的经济性产生了何种影响。Synopsys公司 测试了几款目前在市场上出售的移动多媒体设备,发现目前多数智能手机和平板电脑可以支持用28nm工艺开发的音频编解码器。

本文介绍了测试结果还讨论了将音频功能整合进28nm移动多媒体SoC所面临的商业和技术挑战,同时阐述了如何克服这些挑战的见解。本文还解释了一些关键的设计考虑,包括缩放限制、电源电压的要求和系统划分选择等。

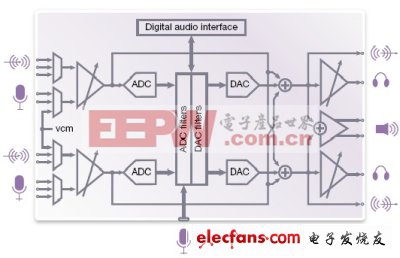

音频编解码器基础:为解释清楚和便于讨论,可使用下图1描述的一款音频编解码器。音频编解??码器包含麦克风和线输入、信号流送和混合、放大器模块、 多通道ADC和DAC。它还包括各种输出驱动器,包括线输出、耳机和扬声器驱动器以及一个包含抽取/插值滤波器的小数字信号处理模块和一个标准的I2S数 字音频接口。

图1:典型的音频编解码器方框图。

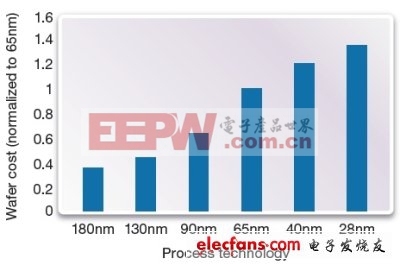

28nm工艺技术的成本考虑:在28nm工艺技术,晶圆成本比65nm技术高得多。对遵循摩尔定律的数字电路来说,更高的晶圆成本可以通过增加的门密度、可能整合进更多功能和更高性能予以补偿以证明其物有所值。

模拟电路,诸如广泛使用I/O器件的音频编解码器,不以与主要使用内核器件的数字电路一样的方式随工艺节点的缩小而减小。除非晶圆面积可减少25-30%,否则更高的晶圆成本将显着增加音频技术的整体硅成本。

例如,为保持相同的硅成本,用65nm技术实现的一款2.5mm2的音频编解码器,在用28nm工艺实现时,需要缩小至1.9mm2。下图2显示了到 2013年,每个12英寸晶圆的成本预测(以65nm工艺为标准)。而28nm晶圆的生产成本预计将比65nm晶圆的高近40%。

图2:2013年,不同工艺的晶圆生产成本,以65nm为标准 (资料来源:Selantek公司)。

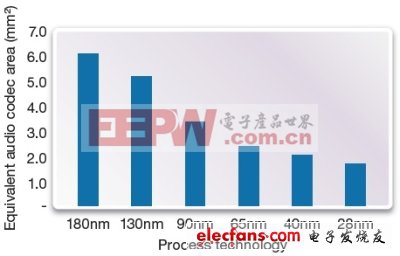

因为与65nm技术实现的相同功能音频电路比,28nm技术的该电路性能并没有显著提升,所以决定是否集成音频功能的关键因素之一是硅芯片的成本。下 图3显示了与用65nm工艺实现的2.5mm2的音频编解码器相比,为保持相同的硅成本,用不同的工艺技术实现所要求的面积。

图3:与用65nm工艺实现的2.5mm2的音频编解码器相比,为保持相同的硅成本,不同的工艺技术实现所要求的面积。

本文以下各节将讨论在28nm工艺几何尺寸,整合音频编解码器的关键技术挑战。每个挑战都可以通过改进电路或系统来解决,以为SoC提供最优化的功耗和成本。

音频编解码器的尺寸缩小限制

有三个主要的电路模块制约着音频编解码器随工艺的发展而缩小:

有源放大器和梯形电阻:有源放大器和梯形电阻用于混合不同音频源的众多音量控制和开关应用中。器件匹配特性制约着有源放大器的性能。减少单个器件的体 积对器件匹配性能产生负面影响并显着降低了有源放大器的性能。基于该原因,与40nm或65nm工艺的放大器相比,采用28nm工艺节点实现相同性能的有 源放大器的面积并不会减少很多。为避免任何可察觉的杂音(如拉链噪音),音量增益步进必须低于1dB。这就需要可变抽头电阻具有大量的抽头,从而增加了总 面积。

数据转换器:大多数的音频编解码器采用Σ-Δ(sigma-delta)ADC和DAC电路实现。开关电容电路的噪音水平与电容值成反比。因此,对于 一个给定的音频性能要求来说,就对应一个所需的最小电容值,所以,电容面积不会随工艺节点的缩小而减小。使问题进一步复杂的是,随着电源电压从 2.5V(或3.3V)降低到28nm工艺的1.8V,为保持相同的动态范围,必须降低噪声水平。所以,电容的面积和容值必须加大。

输出驱动器:必须低失真地提供大输出电流。为了支持驱动耳机和扬声器所需的大输出电流,输出器件必须很大,它也不会随工艺技术的缩小而变小。数据转换 器模块与此一样,如将在下面更详细讨论的,当工作电压从2.5V降至1.8V时,会对输出驱动电路的面积和性能有影响。

以下两节将探讨在28nm工艺、采用1.8V电压实现输出驱动器时的权衡与影响。

工作电压对输出驱动器性能的制约

在65nm和40nm工艺,许多集成的音频编解码器的模拟电路使用2.5V的I/O晶体管且实际上将2.5V器件过驱至3.3V以提高音频性能。然 而,在28nm工艺,大多数SoC设计将转而采用1.8V的I/O晶体管。目前,

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)