通信系统中高性能分集接收机的设置分析

时间:07-19

来源:互联网

点击:

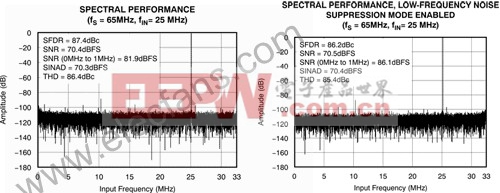

个通道 75mW、9x9mm 封装中,低功耗选项仅占用 81mm^2,也即四个双通道 ADC 板级空间的四分之一。更为重要的是,利用串行 LVDS 数据接口后,每个 ADC 通道只需一个 LVDS 对。增加一个 LVDS 帧和位时钟并利用 20 条物理线路(10 个LVDS 对)便可以在 FPGA 中对八个 ADC 的数据进行处理,并占用最少的板级空间。1/f 噪声出现在基带上,其常见于针对 CMOS 低功耗而设计的 ADC 中。这就限制了基带上(即 ZIF 架构要使用 ADC 的地方)的有效 SNR。ADC 具有一个抑制基带 1/f 噪声的可选模式(请参见图 2)。

图 2 请注意,一旦该模式被激活 1/f 噪声(基带附近)便被转换为奈奎斯特,并且两种情况下均可看到 0-1MHz 的 SNR根据奈奎斯特 (32.5MHz) 测得 65MSPS 下 ADS5282 的 SNR 为 70.4dBFS。如果假设噪声底限较奈奎斯特扁平,那么 0-1MHz 频带中的噪声功率则为 85.5dBFS,这主要是由于 15.1dB 的处理增益:10log10 (32.5M/1M)。利用能够过滤高达 1MHz 的信号和噪声的理想滤波器,85.5dBFS 就为数字滤波器输出的预期 SNR。但是,1MHz 频带中测得的 SNR 为 81.9dBFS,因为基带上存在 1/f 噪声。一旦噪声抑制模式被激活,该频带中测得的 SNR 便提高到 86.1dBFS。1MHz 带宽中测量值(86.1dBFS)超出预期值(70.4+15.1=85.5dBFS)的这一事实具有误导性,因为它是由一个标准奈奎斯特 SNR(70.4dBFS)计算得到的,而该奈奎斯特SNR 包括了高阶谐波(第九阶以上),其被当作了噪声。这表明,真正的奈奎斯特 SNR(所有谐波除外)实际上高于 0.6dB,或为 71dBFS。该 ADC 还在每条通道内提供了两倍抽取功能,以消除移频 1/f 噪声(仍然出现在 Fclk/2 附近),通过处理增益改善带内SNR,并且降低高速串行 LVDS 数据速率。所用数字滤波器保持少量的抽头,以达到节能的目的。这样,使用抽取滤波器时处理增益为 ~2dB。通过使用抽取功能来降低 LVDS 速率后,可考虑使用更低成本的 FPGA 选项,同时在 ADC 和 FPGA 之间拥有更为轻松的时间预算。总结

满足蜂窝网络规范要求的 BTS 并不是一项全新的成果。大多数新型 BTS 设计的主要目标都是想通过降低 BTS 构建成本或减少 BTS 构建数量来降低运营商的成本。其中,射频成本只是构建蜂窝基站总成本的一部分,因此如果它们可减少构建基站的数量,那么就应该对射频接收机设计进行改进。通过构建更为灵敏的射频设备,覆盖相同区域所需的基站数量更少。运用具有高度集成的 ZIF 接收机和一个八通道 ADC 的分集接收机使可实现一个更少空间占用、更低成本和更少组件数量的高性能系统。

- ADC前端电路的五个设计步骤(04-27)

- ADS58C48 切换模式在时分通信系统中的应用(11-13)

- 通信系统关键的AD器件发展情况及瓶颈(09-24)

- 差分滤波器布线需要注意的8个问题(11-05)

- 通信系统中高性能分集接收机的设置(08-24)