基于ESL并采用System C和System Verilog的设计流程

SystemVerilog

SystemVerilog是一种相当新的语言,它建立在Verilog语言的基础上,并新近成为下一代硬件设计和验证的语言。SystemVerilog结合了来自

Verilog、VHDL、C++的概念,还有验证平台语言和断言语言,也就是说,它将硬件描述语言(HDL)与现代的高层级验证语言(HVL)结合了起 来。由于拥有这样的概念以及它与Verilog的向上兼容性,使其对于进行当今高度复杂的设计验证的验证工程师具有相当大的吸引力。能够采用 SystemVerilog进行验证的另一项成功因素是方法学手册和架构的更早可用性,例如在SystemVerilog的验证方法手册(VMM)(见参 考文献[2])中所描述的验证平台方法(这一方法是由ARM和Synopsys合作开发的)。

上述这些特点,以及SystemVerilog是一项得到了所有主要EDA供应商支持的IEEE标准的事实,使得SystemVerilog实质上成为了硬件设计和验证的首选语言。

SystemC与SystemVerilog特点比较

就SystemC和SystemVerilog这两种语言而言, SystemC扩展了C++在硬件方面的适用范围,而SystemVerilog扩展了Verilog在基于对象和验证平台方面的适用范围。而这两种语言 均支持诸如信号、事件、接口和面向对象的概念,但每一种语言又均拥有自己明确的应用重点:

●SystemC对于体系架构开发编写抽象事务处理级(TL)模型、或执行建模来说最为有效,特别是对于具有很强C++实力的团队和有基于C/C++ IP 集成要求(如处理器仿真器),以及为早期软件开发设计的虚拟原型来说,更是如此。

●SystemVerilog对于RTL、抽象模型和先进的验证平台的开发来说最有效率,因为它具备了执行这方面任务所需的基础架构,例如受限制随机激励生成、功能覆盖或断言。

●SystemVerilog显然是描述最终的RTL设计本身的首选语言,不仅在于其描述真实硬件和断言的能力,还在于对工具支持方面的考虑。

这并不意味着每种语言不可以用在不同的应用中。 实际上,SystemC可以用于验证平台和描述RTL结构,而SystemVerilog也可以用于编写高层事务处理级模型。但是,每一种语言都用于自己 的重点应用时,它们可以达到最佳的效率。这点对于复杂的项目特别适用,在这种项目中,不同的任务分属于不同的组,通常有不同的技能要求。注重实效的解决方 案以及符合设计团队的多种技术要求的方法是同时使用SystemC和SystemVerilog来开发和验证当今设计流程需要的虚拟原型的事务处理级模 型。

集成的仿真环境

将SystemC和SystemVerilog集成在同一个解决方案中,归根结底是需要提供混合SystemC和SystemVerilog的仿真和 调试环境。这项集成的核心在于能够直接从SystemVerilog任务中调用SystemC成员的能力,反之亦然,可以从SystemC成员中直接调用 SystemVerilog任务。很明显,这样就要求在SystemC和SystemVerilog的时间概念之间达到同步。

为了建立SystemC和SystemVerilog的高效集成解决方案,让诸如信号和事务处理这样的基层概念在语言设计中,尽管已经在各自的语言中 进行了各自方面的优化,在语义上又能够跨越语言分界实现有效的映射。实际上,SystemC和SystemVerilog的标准化组织,OSCI和 Accellera,已经认识到在这两种语言之间建立有效接口连接机制的需求。

SystemC和SystemVerilog集成的核心支持了混合层级结合的建模,而有能力创建部分处于事务处理级和部分处于具体硬 件级的仿真模型。因此,集成让SystemC和SystemVerilog能够在不同的抽象层级上进行通讯。

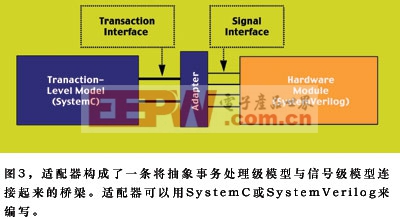

一个典型的应用实例是将一个SystemVerilog RTL模块集成到整个系统的一个SystemC模型中,例如,为了实现早期集成检查。由于SystemC典型情况下应用在事务处理级,就有必要使用一个作为抽象层级之间桥梁的适配器(图3)。

这些适配器的目的在于将事务处理转换成信号操作,而反之亦然。这样,就可以让设计的一部分在事务处理层次上进行仿真,而另一些部分在具体硬件层级上进行仿真。采用这种方法,设计人员拥有对于仿真具体层级的完全控制。

这些适配器可以用SystemC或以SystemVerilog(图3)来编写。使用一项SystemC适配器是相当直接的方式,并且以将 SystemC信号映射到SystemVerilog信号为基础,反之亦然。而以SystemVerilog来缩写转换器时,典型情况下能够提供更高的性 能,但要求在SystemC与SystemVerilog之间建立事务处理级接口。

SystemC与SystemVerilog之间的事务处理级接口

在System

C中,将通讯与功能区隔开来的目的导致了接口概念的形成。在SystemVerilog中,与接口类似的概念也进行了设计。虽然 SystemVerilog接口和SystemC接口并不完全一致,它们在语言上具有足够

- 高效率升压转换器是延长电池使用寿命的关键(09-30)

- 赛普拉斯设计首款背面照明、数字输出的CMOS 图像感应器(05-26)

- 基于SystemView的数字频率合成器的设计(10-31)

- SystemVerilog设计语言(11-02)

- PCM串行数据流同步时钟提取设计(02-25)

- 一种数模混合SoC设计协同仿真的验证方法(04-09)