数字音频传输系统方案设计与实现

1 引言

随着电子技术和数字化技术的飞速发展,数字音频已经在广播电视的录制、播出、传输等各个应用领域得到了广泛的应用。在很多场合,模拟音频已经无法适应整个扩声系统最基本的要求。大型体育场扩声系统设计中极为关键的问题是如何解决微弱的音频信号的远距离优质传输。对于大型场馆,需要传送的距离通常达到几百米远。采用传统的模拟传输方式,难以解决信号损耗和电磁干扰及接地干扰等难题。数字音频的各种性能远远优于模拟模式,因此广播电视设备的数字化已经成了必然的趋势。采用数字信号进行传输和处理的优点是数字信号对干扰不敏感,整个系统的信噪比及失真与传输距离无关,对于长距离传输,其优良的性能指标是模拟传输所无法比拟的。

目前无论电台还是电视台的演播室都在朝着数字化方向发展,作为数字化电视制作的主要功能手段,数字音频的基本理论、接口方式、音频格式和系统设计同样成为广播电视节目制作领域的重大课题。然而,当前绝大多数高性能的数字播出、传输设备都是进口设备,且价格昂贵。本文研究设计的正是应用于这一领域的一款高性能数字音频传输系统。

2 数字音频接口标准

目前常用的数字音频接口标准主要有AES/EBU(AES3 - 1992)接口、S/PD IF接口、MAD I接口等。S/PD IF主要是作为民用数字音频格式标准,MAD I接口是以双通道AES/EBU 接口为基础而制定的,在专业数字音频领域中主要使用AES/EBU接口标准。

AES/EBU的全称是Audio Engineering Society/Eu2ropean B roadcast Union (录音师协会/欧洲广播系统联盟) ,现已成为专业数字音频较为流行的标准,大量民用产品和专业音频数字设备如CD机、DAT、MD机、数字调音台、数字音频工作站等都支持AES/EBU。

AES/EBU标准是AES和EBU一起开发的一个数字音频传输标准,它是传输和接收数字音频信号的数字设备接口协议,规定音频数据必须以2的补码进行编码。传输介质是电缆,允许高带宽容量和由A /D转换器产生的并行数据字节的串行传输。在串行传输16~20 bit的并行字节时先传输最低有效位,必须加入字节时钟标志以表明每个样值的开始,最后的数据流为双相标志码编码,另外时钟信息也内嵌进了AES/EBU信号流中。

AES/EBU通过基于单根绞合线对来传输数字音频数据,使用串行位传输协议,无须均衡即可在长达100 m的距离上传输数据。它提供两个信道的音频数据(最高24比特量化) ,信道是自动计时和自同步的。

它也提供了传输控制的方法和状态信息的表示( chan2nel status bit)和一些误码的检测能力,它的时钟信息是由传输端控制,来自AES/EBU的位流。

AES/EBU的普通物理连接媒质有: ( 1)平衡或差分连接,使用XLR (卡侬)连接器的三芯话筒屏蔽电缆,参数为阻抗110Ω,电平范围0. 2 ~5 Vpp,抖动为±20 ns。(2)单端非平衡连接,使用RCA插头的音频同轴电缆。(3)光学连接,使用光纤连接器。

AES/EBU自1992年修订以来,该标准已经在录音制作、数字影院和广播电视行业广泛应用,成为最常见的数字音频格式,相关设备、接口、线缆、配件等应有尽有,而且价格低廉。

3 系统电路设计

3. 1 系统的总体方案

整个数字音频传输系统分为发送端、接收端和传输介质(电缆) 3个部分,如图1所示。传输介质主要有双绞屏蔽线电缆、同轴电缆、光纤和无线传输(如PDH或SDH数字微波) ,根据具体场合及传输距离来选用。

图1 数字音频传输系统原理框图。

发送端主要是完成对信号的接入、A /D 转换、格式编码、时钟产生等工作。为了增加信号的动态范围,同时防止A /D转换中出现混叠失真,在模拟输入通道中应设置信号调理电路和抗混叠滤波器。

接收端主要是完成对AES/EBU 格式数据的接收、解码,恢复出主时钟信号、同步信号,再对音频数据进行D /A转换等工作。

3. 2 发送端电路设计

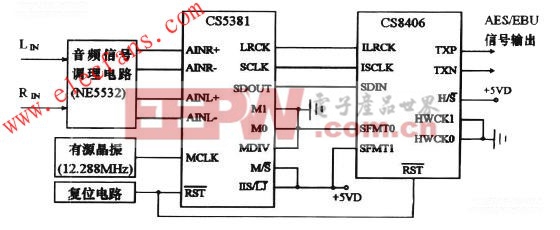

根据前节所述的系统方案,我们选用Cirrus Logic公司的CS5381和CS8406分别完成模拟信号的A /D转换和AES/EBU格式编码发送,电路原理如图2 所示。

图2 发送端原理图。

CS5381是CirrusLogic公司推出120 dB、192 kHz高性能24 bit立体声模数转换芯片。CS5381可工作在主、从两种模式下。模式选择可通过管脚2 (M /S)来进行,本设计工作在主模式。CS5381采样率可以通过MD IV、M0和M1这3个管脚逻辑电平控制,主时钟选择可以根据所选的采样频率和MD IV引脚作选择。本设计中选择的是48 kHz单倍速采样率,采用12. 288MHz有源晶振做时钟源。CS5381转换结果是24位补码形式串行数据,且左右通道交替输出,可用LRCK高低电平来进行区分。输出数据有两种格式即左对齐和I2S格式,本设计采用I2S格式。

- 基于DPPC2006的数字音频功率放大器(05-05)

- 基于混沌同步信号自适应传输的数字音频加密(03-09)

- 利用Microchip开发工具包和软件轻松实现iPod和iPhone配件开发(03-02)

- 数字音频传输系统的设计与实现(03-23)

- 数字音频技术知识点及声卡驱动(02-14)

- 基于nRF24Z1的CD音质无线数字音频传输系统(11-02)