基于EPG3231和闪存的声音播放器设计方案

摘要:提出一种在单片机系统中比较简单地使用大容量NAND FLASH存储器的方法。与一般方法相比,编写应用程序的程序员不需要掌握计算机文件系统的规范,只要按照NAND FLASH的读、写、擦除等时序对其进行操作,把NANDFLASH当成NOR FLASH或SRAM来对待,这样存储器的物理地址对程序员而言是透明的,只需要在遇到坏块(BAD BLOCK)时跳过该块就可以了。该方法降低了使用NAND FLASH存储器的难度和成本,且不仅适用于EPG3231,也可以推广到一般的8位单片机系统中使用。

在从事单片机的教学中,由于学生对有声音和显示的制作项目更感兴趣一些。因此,在学习过程中这种兴趣往往能让他们完成项目,获得成就感,从而学到更多的东西。

目前在技术上,声音的存储大都使用大容量的NAND FLASH,但一般按照文件系统的方式存储,这对学生有一定的难度。本声音播放器的声音文件采用非文件方式存储在NAND FLASH中,这样在不需要太多背景知识的情况下,可以比较简单地使用大容量的NAND FLASH存储器,降低了使用NAND FLASH存储器的难度和成本。

1 声音播放器总体设计方案

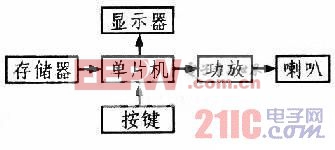

声音播放器总体设计框图如图l所示。其中存储器用于存放声音文件,单片机将存储器中的声音文件名显示在显示器上,并根据按键选择要播放的声音文件,从存储器中将声音文件的数据送到内部的D/A转换器,D/A的输出通过功放放大后送到喇叭放出声音。

图1 声音播放器总体设计框图

其中,在选择存储器时,应满足大容量、非易失、价格便宜等条件,根据上述条件,NAND FLASH为最佳选择,这里选用K9G8G08型NAND FLASH,其容量是1 G字节。对于WAV格式的语音信息,8 bit、22.05 kHz、单声道足以满足一般需求,而对于音乐(歌曲)来讲,44.1 kHz的采样频率也能达到较好效果,因此,该器件中能存储约800 min语音或400 min音乐;显示器采用122x32的LCM,内置控制器为SEDl520,可以显示14个汉字或28个英文字符;按键主要有放音/暂停、停止、上翻、下翻等,采用独立式按键;单片机选用ELAN的EPG3231,该器件与5l系列单片机使用相似。

设计声音播放器关键需要考虑:声音数据以何种格式、何种方式载入K9G8G08。一种可直接用一个U盘,通过计算机将数据下载到K9G8G08中,声音数据以文件方式存放。但这样必须在单片机中完成与U盘的接口连接,并且要熟悉计算机的文件格式,这对单片机的初学者来讲难度比较大。另一种是将声音数据按顺序存放在K9G8G08中(遇到坏块时跳过即可),这样数据存放的物理地址对开发者来讲是透明的,再使用下载器就可以将声音数据载入K9G8G08中。如果将下载器和声音播放器做在一起,同样可以在线下载数据。

2 声音播放器硬件电路设计

2.1 K9G8G08简介

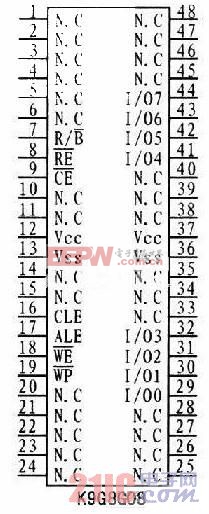

K9G8G08是三星公司生产的1 Gx8 bit的NAND FLASH存储器,工作电压为2.7~3.6 V,内部存储结构为(2 K+64)字节/页×128页/块×4096块。外部电路通过共用的8位I/0端口分时访问其命令寄存器、地址寄存器和数据寄存器,实现对器件读、写和擦除等操作。其存储器的命名方式参见文献。K9G8G08采用48引脚的TSOP封装,其引脚配置如图2所示。

图2 K9G8G08引脚配置

2.2 EPG3231简介

EPG323l是ELAN公司的8位RISC单片机,它有11个8位并行口、1个8位电流输出型的D/A、1个10位逐次逼近型A/D、1个通用异步收发器UART、1个8,16,24位的串行外设接口SPI、3个定时器等,硬件资源丰富,还支持手写识别、语音识别、ADPCM编解码等功能。另外,EPG3-23l的速度较快,在时钟频率为16 MHz时,指令周期为125 ns。

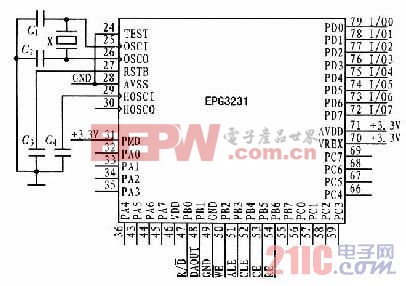

2.3 EPG3231与K9G8G08的电路连接

图3为EPG3231与K9G8G08的电路连接图。图中没有给出K9G8G08,只给出了EPG323l的基本电路及用网络标号标出的与K9G8G08的连接引脚。K9G8G08的19引脚是写保护,在实际电路中接+3.3 V(不保护)。需要说明的是,EPG323l的D/A输出是48引脚(PBl),输出电流信号,需要将其输出转换为电压信号再送至后续的功放。其中比较简单且可行的做法是在PBl与地之间接一只电阻来完成电流与电压的转换,关键是该电阻的取值。若电阻阻值较大,输出波形的上部会出现限幅失真;若阻值较小,则不能最大限度地利用D/A的动态范围。因此确定该电阻阻值的方法是:先接一只可调电阻,写一段测试程序,向D/A反复连续地送00~FFH的数值,通过示波器观察PBl输出,调整可调电阻,使输出为不失真的锯齿波,且最高点为3.3 V(即参考电源VREX(70引脚)电压)。

图3 EPG3231与K9G8G08的电路连接图

另外,图3中使用EPG323l的D端口(PD0~PD7)与K9G8G08的I/O端口相连,这个端口必须是双向的,使用其他的双向端口也可以

- 工作在扩展温度范围的计时器件(11-13)

- 基于DS3231的高精度时钟接口设计(03-21)

- Maxim DS3231实时时钟应用笔记、使用指南、FAQ全集(02-14)

- 确保USB驱动器安全:风险产生原因和应对之策(08-10)

- 闪存电源原理图分析设计(02-10)

- 非易失性存储器主导闪存发展的关键技术(05-27)