12位A/D转换器ADS7864在电网谐波分析仪中的应用分

在许多相关文献中,为保证DSP运行速度与A/D转换器响应速度相匹配,往往采用片内I/O口与A/D转换器接口,依靠软件实现A/D转换器的片选(CS)与数据读取控制(RD),这种方式虽然可保证操作的可靠性,但同时也占用了DSP上的I/O口资源,而且具有接口连接的A/D转换器数量非常有限。

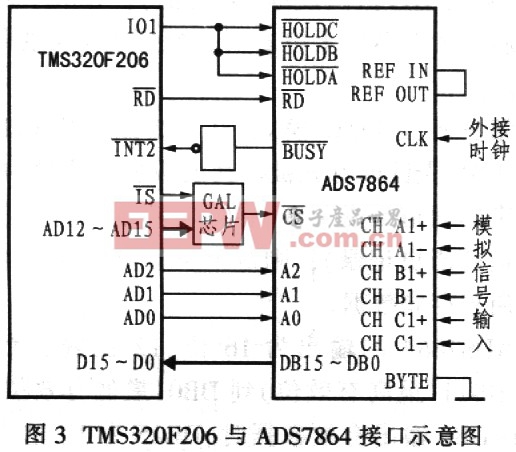

经过仔细分析,在电网谐波分析仪的硬件设计中F206与ADS7864仍然采用了传统的地址译码片选的接口方式,将F206的I/O空间选择端IS与地址线ADl2~ADl5先输入可编程逻辑器件GAL22V10,再输出片选信号CS。F206的RD端直接与ADS7864的读数据控制端RD端连接。

由于F206外部数据总线为16位,可将ADS7864的输出数据宽度控制端BYTE接地,16位输出直接与F206的数据总线相连。

由于在电网谐波分析中要求同时对三相电压、电流信号进行采样,所以ADS7864的采样保持启动控制端HOLDA、HOLDB、HOLDC直接与F206的I01端连接,当I01输出低电平时,同时启动三组6路信号的采样保持并进行转换。

在谐波分析仪的设计中,ADS7864的数据读取采用地址模式,每次转换结束后,由ADS7864的BUSY端通过反相器向F206的INT2端发出中断信号,完成一次6路信号的采样转换共响应3次中断,在每次中断服务程序中读取相应地址的转换数据。

5 结束语

根据笔者长期的设计体会,在DSP与A/D转换器接口的硬件与软件设计过程中,有几个带有共性的问题需要引起足够的重视:

(1)地址建立时间对接口的影响

在微处理器系统中为保证正确读取数据,在读数据控制信号RD有效前,需要提前建立地址总线信号,这一时间称为地址建立时间。在40 MHz主频时,F206的地址建立时间最小值为8.5 ns,而ADS7864要求的地址建立时间至少为10 ns(使用8MHz外部时钟时,下同)。显然,由于地址建立时间的约束,F206在40 MHz主频时不能采用传统的地址译码片选方式与ADS7864接口,为保证时序的要求,必须使用I/0口。

当F206工作在20 MHz主频时,地址建立时间为2l ns,则可以采用传统的地址译码片选方式与ADS7864接口,这也是本文实际应用的接口方式。

(2)数据建立时间对接口的影响

为保证微处理器可靠地读取数据,在距读数据控制信号RD上升沿一段时间时,数据就应稳定地出现在数据总线上,这一时间称为数据建立时间。在ADS7864中,要求读数据控制信号RD和片选信号CS在输出数据有效前必须保持低电平至少30 ns,但是当工作在20 MHz主频时,F206的读数据控制信号RD所能提供的数据建立时间在20 MHz主颍时最少为30 ns,显然是不能可靠满足要求的,必须使用F206的软件状态等待发生器来产生等待信号以读取数据。

综上所述,在DSP与A/D转换器的接口设计中,只要仔细分析并充分考虑DSP运行速度与A/D转换器响应时间之间的关系,并充分发挥DSP上软件等待状态发生器的作用,完全可以采用传统的地址译码片选方式实现DSP与A/D转换器之间的可靠接口,从而节约宝贵的I/O口资源。

- 12位500kHz六通道同时采样的A/D转换器ADS7864及其(08-31)

- 稳定低噪声放大器中晶体管工作点的设计方法(下)(11-20)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 用ADS实现一个2.38GHz全集成化低噪声放大器设计(04-26)

- 基于ADS8364的数据采集系统设计(10-01)

- 发夹型滤波器的设计(10-23)