用于移动宽带基础设施的新一代无线电数字前端解决

网络运营商在通过使用新型空中接口、更高带宽和更多蜂窝基站努力扩大网络容量的同时,要求显著地降低设备成本。为提供能够满足所有这些需求的设备,无线基础设施设备的制造商正在寻求具有更高集成度、更低功耗和成本但灵活性更高的解决方案。本文将分析赛灵思提供的新型器件Zynq™可扩展处理平台(EPP)将如何帮助设备制造商解决这些问题。

智能电话、平板电脑和数据集线器的普及正推动无处不在的高速数据需求呈爆发式增长。为提供这种数据满足他们的需求,网络运营商不得不使用LTE或者LTE-A等最新空中接口标准,构建更多蜂窝基站,同时增加每个基站的天线数。另外,每用户平均收入(APRU)的持续下降使运营商每年都要求设备厂商大幅降低成本。更糟糕的是,这些新的蜂窝基站网络可能要求扩展现有的语音和数据网络,而现有网络采用GSM或UMTS标准且部署在不同的频段上。

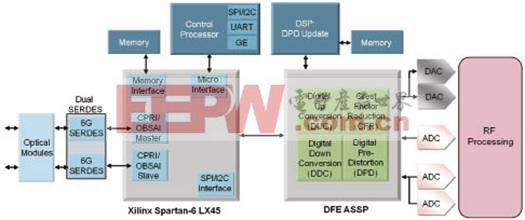

图1 典型无线电设备的高级方框图

不管是增加天线数量来支持多个频段,还是采用多输入多输出(MIMO)技术提升数据速率,虽然成本高,但对运营商来说是必要的。为降低对天线杆相关运营成本的影响,设备制造商正在想法设法缩减设备的封装尺寸(即设备的体积和重量),同时还要降低成本和功耗。他们在无线电传输领域不断创新,从天线到双工/三工器乃至无线电设备本身,努力缩小天线杆的封装尺寸。

运营商可以采用多种方案满足自己的需求。其中之一是使用多频段天线,从而减少为支持基于GSM、UMTS或者LTE的多个网络所需的天线数。为进一步完善这些多频段天线,运营商可在天线杆上安装远程无线电装置,为所需的频段提供支持。远程无线电装置也必须不断发展,以支持多种空中接口和更高的带宽,同时减轻重量,缩小机箱,才能满足运营商的未来需求。

天线集成无线电装置的兴起,为运营商提供了又一种可选方案。这种方法把无线电电子装置安装在天线机箱中,实现全集成的无线电和天线,故不必采用单独的远程无线电装置,从而最小化了天线杆尺寸。无线电电子装置和天线机箱的进一步发展就是最近推出的有源天线系统(AAS)。这种复杂的天线要求更强大的无线电信号处理能力,可增加网络容量,同时缩小天线杆的封装尺寸。

缩小远程无线电装置或天线的尺寸和重量的关键之处在于进一步提高无线电电子装置的集成度。另外,为了支持GSM、LTE、UMTS等多种空中接口,无线电设备必须具有高度的灵活性和可编程功能。

先来看看这些无线电设备如何才能具有更好的可编程性,同时又能提供更高的集成度。

图2 典型的基于ASSP的2x2无线电设计

图3 赛灵思提供的新型Zynq EPP系列

图4 利用 Zynq实现的2x2 LTE无线电

基带接口的作用是通过基带处理卡把系统连接到铜光纤上。基带处理卡的位置可以在天线杆的基座上,也可以在空中。这些接口一般需要借助运行速度高达9.8Gbps的高速串行/解串器(serdes)组件,才能用作通用公共无线接口(CPRI)。

基带单元上接收到的信号或发送给基带单元的信号在发送到模拟域之前或从模拟域接收到之后,需要进行大量的信号处理。信号处理包括数字上/下变频(DUC/DDC)、峰值因数抑制(CRF)和数字预失真(DPD)。DUC和DDC负责处理上采样和整形,而CRF和DPD主要用于通过采用数字信号处理线性化功率放大器,来提高无线电单元的传输效率。

采用高速并行LVDS信号发送或新兴的协议JESD204[A/B]均可实现到数据转换器(DAC和ADC)的接口。

射频(RF)领域包含所有的调制器、时钟综合装置、滤波器和放大器电路,用于经功率放大器从天线处发送和接收数字信号。

整个无线电电装置采用微处理器进行控制。该微控制器一般运行在Linux或VxWorks等实时操作系统上。运维功能负责无线电单元的告警、校准、消息发送和整体控制,这是一项复杂的工作,一般需要连接SPI/I²C、以太网、UART(当然还包括存储器)等其它众多组件。

过去供应商综合运用ASIC、ASSP和FPGA器件来实现数字无线电信号处理功能。ASIC器件的灵活性最差,一般会因设计初期规格锁定而导致功能缺失。虽然该器件成本最低,但开发和NRE成本高,且产品上市速度慢。ASSP器件灵活性有限,因为它们往往是针对一系列使用案例而设计的,不适用于其它应用。而FPGA则不然,由于其内在的高灵活性,在数字无线电领域的应用正在不断增长。FPGA能支持各种设备需求,同时能够根据客户需求的发展变化不断交付新功能。在这类应用中的许多案例中,FPGA紧邻ASIC和ASSP器件放置,用于弥补其它器件欠缺的功能。

图2说明了综合使用ASSP、FPGA和微处理器构建的2x2的无线电设备。

ASSP一般适应市场需求的速度较慢,这在它们缺乏任何像CPRI或JESD204这样的串行接口技术可以看出。这就需要一个辅助器件,比如内置有串行解串器的FPGA或使用外部串行解串器的低成本FPGA来完善设计。但这种设置需要大量的组件,从而导致PCB占位面积大,电源高度复杂,总功耗和成本都很高。

图3所示的Zynq EPP采用双ARM® Cortex™-A9处理器内核(每个内核的整数运算性能高达2000MIPS)和一个双精度浮点单元。处理器子系统包含存储器控制器、千兆位以太网、UART和SPI/I²C等专用通信外设。紧邻处理器子系统的是高性能可编程逻辑,其内含500MHz DSP模块、12.5Gbps串行解串器和大量的内部RAM。多条低时延、高带宽总线用于连接处理器子系统和可编程逻辑,同时共享存储器接口可保证避免发生性能瓶颈。

图4所示的是设备制造商如何利用Zynq实现当今远程无线电装置中的全部功能。

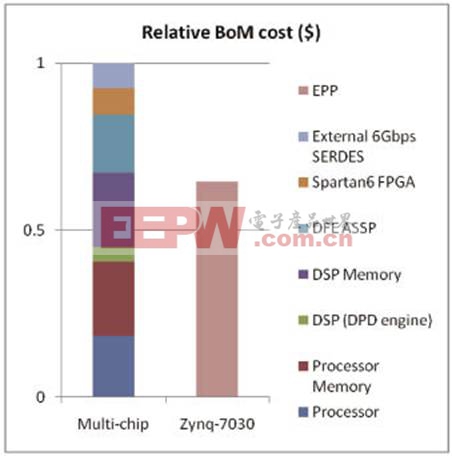

从图5和图6可以看出与现成的ASSP相比,这种架构能够实现明显的成本和功耗节约。这个示例假定信号带宽为20MHz,有两个发送和两个接收路径。Zynq还能够支持更高的带宽和更多数量的天线。

在2x2 20MHz LTE示例中,Zynq解决方案将功耗降低了高达50%,总材料成本相对等效ASSP设计降低了 35%~40%。另外,图7还显示,由于较图2元组件数量减少,在提供图4中相同的功能时,封装面积可缩减达66%。

图5 使用Zynq相对降低材料清单(BOM)成本

图6 使用Zynq降低耗电

图7 使用Zynq缩减封装面积

使用Zynq还可以降低电源的复杂性和成本,同时提高无线电单元的可靠性。可靠性的提高能够减少对市场退货相关的后期执行费用的影响,还能够实现更高的网络可靠性。另外降低功耗还能够减少散热,从而可以使用尺寸更小、重量更轻的散热器和机械结构。最后,Zynq解决方案能够结合软硬件灵活性,在设计后期才确定无线电单元的规范。这样可以缩短产品上市时间,降低风险,在设备出货后很长时间内还能支持新功能。

- 什么是光伏效应?(01-19)

- 电池的基本知识(01-02)

- 电路设计基础知识--变压器(01-29)

- 功率MOSFET基础知识(02-21)

- 电源基础知识(05-05)

- Keithley技术文献:半导体C-V测量基础(06-27)