AD9852芯片在原子频标中的应用简介

引言

被动型铷原子频标中,综合器模块完成以下功能:

(1) 量子系统作为一个鉴频器,基态87Rb原子0-0跃迁的中心频率为6834.××××MHz,其中尾数部分××××频率由综合器产生。

(2) 为了实现微波磁共振探测,需要在微波信号上加一个键控小调频(调制频率为几十或上百赫兹),这项功能亦由综合器来完成。

(3) 此外,对量子鉴频信号做同步鉴相时,需要提供同步鉴相参考信号且可移相,此项功能也由综合器完成。

在综合器的研发工作中,实际采用了一微处理器与AD9852配合使用,构成综合模块。微处理器完成产生同步鉴相参考脉冲与79Hz键控调频方波信号的功能,通过将微处理器产生的方波信号引入DDS的键控调频引脚,由DDS产生5.3125MHz键控调频信号,经滤波后,送入后续混合电路环节中。

物理机制

在一台实际的被动型铷原子频标中,由于各种因素的影响,原子谱线不可能是绝对对称的,尽管压控晶振的频率输出经射频倍频、综合、微波倍频混频后获得的实际频率可以精确等于谱线的峰值频率,但由于实际谱线不对称,经过伺服环路对量子系统输出鉴频信号的处理后,输出的纠偏电压中就具有调频频率的基波分量,该基波分量是一个伪误差电压,会使压控晶振频率拉偏,如图1所示。

图1 量子系统鉴频输出示意图

若方波调频的深度保持不变,则这个频移量也不变,但是由于传统铷频标中采用了变容二级管调制电路,变容二级管是温敏元件,环境温度变化时,不可避免地将造成方波调频深度发生变化。显然,当方波调频的深度增加时,附加频移量增加;当方波调频的深度减小时,附加频移量减小。因此,铷频标中的谱线不对称,将会通过调制电路给铷频标带来温度系数。故在设计时,将调制电路从变容二极管调制方式改为DDS键控调频调制方式。

直接频率合成

AD9852主要由参考频率源、相位累加器、波形存储器(正弦函数功能表)、数模转换器及低通滤波器组成。参考频率源为DDS提供工作时钟频率,DDS输出的合成信号的频率稳定度在不考虑内部诸如附加相位噪声等环节的影响时,和参考频率源是一样的。

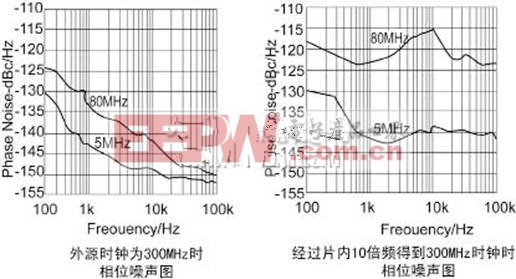

在频率变换器件中,100Hz和1kHz处的相噪是比较关键的技术指标,对用DDS做成的综合器而言,它取决于DDS输出信号的相噪、滤波环路的性能以及放大电路的附加相噪等,其后两项是根据实际设计的滤波及放大电路决定的,对于第一项则取决于实际采用的芯片种类。图2为一款DDS的输出相噪图。

图2 DDS相噪对比图

由图2可见,采用内部倍频的方式在偏离1kHz、输出5MHz时相噪为140dBc/Hz;若直接采用300MHz的时钟时,相噪的性能在偏离1kHz时为142dBc/Hz。因此,为了提高DDS输出信号的相噪性能,采用外部倍频法是一个比较好的选择,即把输入时钟信号在外部进行N倍频后加到DDS上。

DDS在使用时,要通过微处理器或CPLD对其信号、数据进行管理控制来实现具体应用中所需要的若干功能,图3为我们选用的一款DDS芯片外围电路示意图。

其中,MCLK引脚接外部时钟源,使DDS的IOUT引脚输出端频率信号的稳定度与外部时钟源一致。对于内部没有PLL倍频环节的DDS芯片,通常MCLK端输入时钟源的频率应高于IOUT端输出信号频率的4倍。如输出信号频率为5.3125MHz,那么MCLK时钟端的信号频率应该大于20MHz,以期望得到更好的相位噪声,通过外部滤波电路后,可得到比较纯净的信号谱。FSELECT为键控调频信号输入端,也就是我们的调制方波79Hz信号输入端,我们使用的DDS内部有两个频率控制寄存器,通过编程的方式将预先设置好的频率值F0、F1保存在寄存器中,当FSELECT端有有方波信号输入时(即电平上升沿或下降沿转换),DDS的IOUT端将会随之分别从频率控制寄存器中读出F1或F0的值作为输出,并且会保障频率信号在切换时相位无变化。PSEL1、PSEL0为两路信号频率F1、F0的相位调节端,在应用中,如果需要保持F1、F0在切换时的相位连续,需要在设计中直接将PSEL1、PSEL0接地。DDS与外界通讯的时序是通过引脚FSYNC、SCLK、SDATA来完成的,其串行通讯的时序如图4所示。

当FSYNC为高电平时,SCLK、SDATA引脚为高阻状态。当FSYNC为低电平时,DDS将处于通讯状态。此时引脚SCLK有一下降沿的脉冲时,将使挂在数据总线SDATA上的DATA写入DDS数据缓冲区,直至最终一个DATA写入时,DDS将根据引脚FSELECT上的状态选择F1或F0作为IOUT端的输出。

信号的产生

本文选用的DDS芯片内部有2个32位频率控制寄存器(F0、F1),对照图4的串行通讯时序,在SDATA端实际需要通信的DATA位就是32位。假设MCLK外部输入时钟频率为20MHz,DDS的最小的频率分辨率为:

IO

- 基于AD9852的基准源设计(01-23)

- 基于DDS芯片AD9852的雷达回波模拟器设计(10-16)

- 原子频标中AD9852芯片的应用(10-15)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 利用GM6801实现智能快速充电器设计(11-20)