如何提高ADC性能 — 全方位学习模数转换器(ADC)

ADC性能提高的建议

虽然ADC看起来非常简单,但它们必须正确使用才能获得最优的性能。ADC具有与简单模拟放大器相同的性能限制,比如有限增益、偏置电压、共模输入电压限制和谐波失真等。ADC的采样特性需要我们更多地考虑时钟抖动和混叠。以下一些指南有助于工程师在设计中充分发挥ADC的全部性能。

模拟输入

要认真对待ADC的模拟输入信号,尽量使它保持干净,“无用输入”通常会导致“数字化的无用输出”。模拟信号路径应远离任何快速开关的数字信号线,以防止噪声从这些数字信号线耦合进模拟路径。

虽然简化框图给出的是单端模拟输入,但在高性能ADC上经常使用差分模拟输入。差分驱动ADC可以提供更强的共模噪声抑制性能,由于有更小的片上信号摆幅,因此一般也能获得更好的交流性能。差分驱动一般使用差分放大器或变压器实现。变压器可以提供比放大器更好的性能,因为有源放大器会带来影响总体性能的额外噪声源。但是,如果需要处理的信号含有直流成份,具有隔直流特性的变压器就不能用。在设计预驱动电路时必须考虑驱动放大器的噪声和线性性能。需要注意的是,因为高性能ADC通常有非常高的输入带宽,因此在ADC输入引脚处直接滤波可以减少混入基带的宽带噪声数量。

参考输入

参考输入应看作是另一个模拟输入,必须尽可能保持干净。参考电压(VREF)上的任何噪声与模拟信号上的噪声是没有区别的。一般ADC的数据手册上会规定要求的去耦电容。这些电容应放置在离ADC最近的地方。为了节省电路板面积,PCB设计师有时会将去耦电容放在PCB的背面,这种情况应尽可能避免,因为过孔的电感会降低高频时电容的去耦性能。VREF通常用来设置ADC的满刻度范围,因此减小VREF电压值会减小ADC的LSB值,使得ADC对系统噪声更加敏感(1V满刻度10位ADC的LSB值等于1V/210=1mV)。

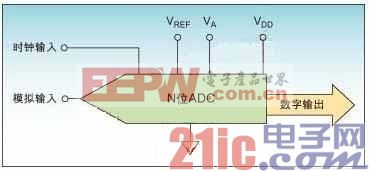

图1:典型的模数转换器功能框图

时钟输入

根据具体的应用,数字时钟输入可能与模拟输入具有同等的重要性。ADC中有两大噪声源:一个是由输入信号的量化引起的(正比于ADC中的位数),另一个是由时钟抖动引起的(在错误时间点采样输入信号)。根据以下公式,在非过采样ADC应用中量化噪声将限制最大可能的信噪比(SNR)值。

其中,N为ADC的位数、SNR为信噪比。

从直观感觉这是有意义的:每增加一位,ADC编码的总数量就会增加一倍,量化不确定性可降低一半(6dB)。因此理论上一个10位ADC可以提供61.96dB的SNR。根据以下等式,采样时钟上的任何抖动都会进一步降低SNR:

其中,SNRj是受抖动限制的SNR,fa是模拟输入频率,tj是时钟抖动的均方根(rms)值。

用抖动等于8ps的采样时钟数字化70MHz的模拟信号,可以得到接近49dB SNR的有限抖动,相当于将10位ADC的性能降低到了约8位。时钟抖动必须小于2ps才能取得等效于10位ADC的SNR。还有许多影响SNR的二阶因素,但上述等式是非常好的一阶接近函数。差分时钟常用来减小抖动。

电源输入

大多数ADC有分离的电源输入,一个用于模拟电路,一个用于数字电路。推荐在尽量靠近ADC的位置使用足够多的去耦电容。尽量减少PCB的过孔数量,并减小从ADC电源引脚到去耦电容的走线长度,从而使ADC和电容之间的电感为最小。就像参考电压去耦一样,电路板设计师为了节省电路板面积有时会把去耦电容放在芯片下方PCB板的背面,基于同样的理由,这种情况也应避免。ADC数据手册一般会提供推荐的去耦方案。为了达到特定的性能,电源和地经常会采用专门的PCB层实现。

数字输出

ADC开关数字信号输出会产生瞬时噪声,并向后耦合到ADC中敏感的模拟电路部分,从而引发故障。缩短输出走线长度以减小ADC驱动的电容负载有助于减小这一影响,在ADC输出端放置串行电阻也可以降低输出电流尖峰。ADC数据手册通常对此也有一些设计建议。

以上我们介绍了什么是ADC,ADC的技术参数指标及误区,并为大家详述了如何提高ADC性能的一些建议。下面我们将继续介绍ADC的一些具体设计中的问题,ADC输入噪声利弊分析、ADC输入转换器电路分析、ADC输入阻抗信号链设计等知识。详述了ADC的设计挑战,如何从高性能转向低功耗,也对ADC的不同类型数字输出进行了深解。

ADC输入噪声利弊分析

多数情况下,输入噪声越低越好,但在某些情况下,输入噪声实际上有助于实现更高的分辨率。这似乎毫无道理,不过继续阅读本指南,就会明白为什么有些噪声是好的噪声。

折合到输入端噪声(代码跃迁噪声)

实际的ADC在许多方面与理想的ADC有偏差。折合到输入端的噪声肯定不是理想情况下会出现的,它对ADC整体传递函数的影响如图1所示。随着模拟输入电压提高,"理想"ADC(如图1A所示)

模拟电路 模拟芯片 德州仪器 放大器 ADI 模拟电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)