ADC输入噪声利弊分析(二)

时间:12-09

来源:互联网

点击:

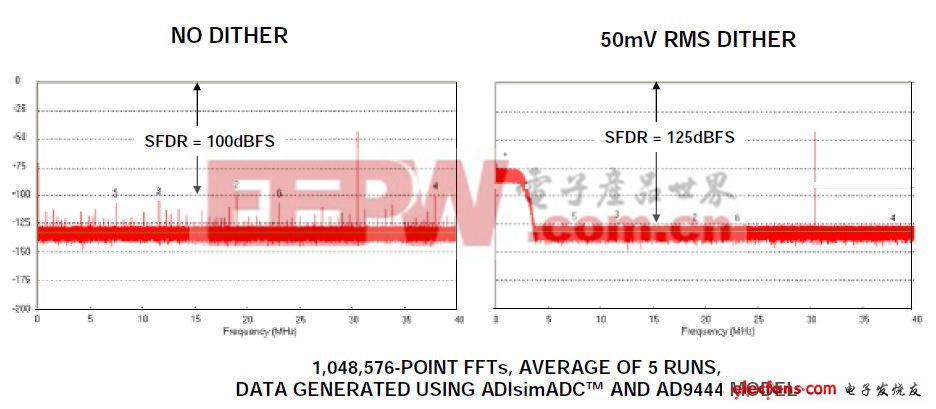

dB.所示数据是利用ADIsimADC程序和AD9444模型获得。 图11:14位、80MSPS ADC AD9444,fs = 80MSPS,fin = 30.5MHz,信号幅度 = –40dBFS 虽然图10和图11所示的结果相当惊人,但不应认为,增加带外噪声扰动一定就会改善ADC的SFDR,或者在所有条件下都适用。正如之前提到的,扰动无法改善ADC前端电路的线性度。即使是近乎理想的前端,扰动的效果也将高度依赖于输入信号的幅度和扰动信号本身的幅度。例如,当信号接近ADC的满量程输入范围时,传递函数的积分非线性可能会成为确定SFDR的限制因素,扰动将没有助益。务必认真研究数据手册,某些情况下,其中可能给出了有扰动和无扰动的数据以及幅度和带宽建议。扰动可能是更新一代中频采样ADC的内置特性。 结束语 在本文中,我们说明了所有ADC都有一定量的折合到输入端噪声。在精密、低频测量应用中,以数字方式对ADC输出数据求平均值可以降低该噪声,代价是采样速率会降低并且需要额外的硬件。该均值方法实际上可以提高ADC的分辨率,但无法降低积分非线性误差。

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)