电容负载稳定性:输出引脚补偿 系列之一

时间:01-31

来源:互联网

点击:

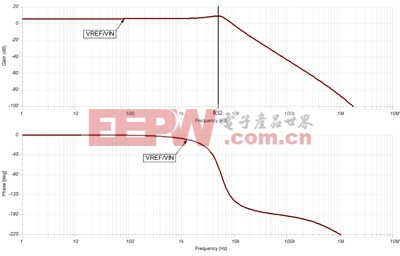

输出引脚补偿 根据图 9.13,我们估计 fcl2 约为 5kHz,因此预计对于 VREF/VIN 而言在该点会出现陡然降低。在图 9.19 中,我们可以看出闭环 AC 响应符合预测结果。在 AC 闭环响应中存在轻微峰化现象,不过其对于本应用不会造成影响。同样,如果我们希望减少这种峰化现象,就需要再次利用我们的输出引脚补偿把 fcl2 点的相位裕度提高到 40 度以上。 图9.19:VREF/VIN AC响应:输出引脚补偿

- 运放电路设计中无源元件的选择(01-23)

- OTL功放电路中的自举电容(01-26)

- DC-DC电荷泵的研究与设计(01-05)

- 为DC/DC转换器选择正确的电感器与电容器(01-02)

- 去耦电容和旁路电容 (10-29)

- 正确选择电容种类优化电脑音质(01-25)