USB 3.0时代如何为接口提速

2012年4月底,随着英特尔发布新一代的ivy bridge芯片组的原生支持USB3.0,更让USB3.0走下神坛。成本的降低让消费者买得起、用得起,普及性大为提升。另外,业界龙头微软将于2012年推出全新的Windows 8,其中装载USB3.0原生驱动程序,这使得USB3.0主控芯片的使用者将获得更好的兼容性,也带动计算机、芯片供应商大规模部署USB 3.0相关产品。尤其是USB 3.0接口大幅了提升USB 2.0接口的效能瓶颈,利用PCIe技术重新取得外部高速接口的规格优势,加上多埠支持的Host芯片技术日益成熟,将在PC和笔记本中大量装载,吸引更多厂商支持USB 3.0高速接口,USB3.0接口将迎来全面普及时代。

目前,市场上各种USB3.0规格的电子产品及外设众多,USB3.0最大传输带宽高达4.8Gbps,传输速度比USB 2.0提升10倍,其最大优点在于USB 3.0保留了即插即用功能并可充当供电来源,且能与USB 2.0兼容,除了为厂商带来更多利润外,也让使用者能够方便升级,并享受其创新功能。除了台式计算机和笔记本电脑等主机端,USB3.0还将应用于各种计算机外部设备,包括U盘、外接式硬盘等。据研究机构IDC的预测,到2015年,USB3.0出货量将加速倍增至23亿,其中50%将应用在存储功能上,这部分市场规模将达到400亿元。业界认为2012年第二季PC与笔记本装载多埠USB 3.0高速接口的比例将大幅增加,其原因一方面是USB 3.0多埠Host芯片解决方案成本持续压低,另一方面则是USB 3.0的外围产品也不再局限于外接硬盘、U盘等产品,预计将会有移动电话、平板电脑、数码相机等推出。

高性能USB3.0物理层IP

智原科技在USB3.0物理层IP的第一个产品就是2008年8月USB-IF协会在Intel举办的IDF上展出的全球第一个USB3.0原型。如图1所示,USB3.0 物理层IP主要包含二大部分:PMA(Physical Medium Attachment Sublayer)和PCS(Physical Coding Sublayer)。

图1:USB3.0 物理层IP主要包含PMA和PCS。

PCS部分主要是进行自动协商(Auto negotiation)及8b/10b编码及解码。自动协商通过两个连接的设备选择常见的传输参数,如速度和流量控制,在这个过程中,所连接的设备首先先各自以自已的最高速传输,再协商找出二边都能支持的最高速作为传输模式。决定传输模式后,PCS即对被传送和接受的信息编码和解码,目的是使接收器更容易恢复信号。

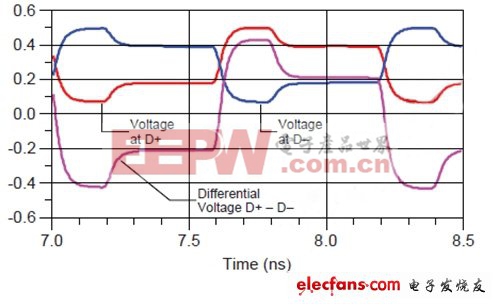

PMA部分主要处理模拟的高速信号,该信号速度高达5Gbps。在传输线方面,USB3.0支持长达3米的四线差分信号线及11英寸PCB。如图2所示,5Gbps信号在长线缆上采用的是差分信号方式传输,从而避免信号被干扰及减少电磁干扰(EMI)问题。PMA电路分为以下六个主要模块。

图2:5Gbps信号采用差分传输可以减少电磁干扰。

并串联(P2S,Parallel to Serial):将较低速的并行信号转成高速的串行信号。

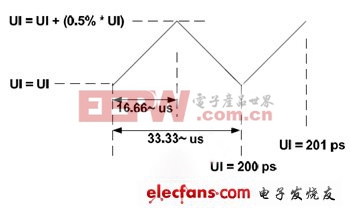

展频频率产生器(SSCG,Spread Spectrum Clock Generator):如图3所示,在5Gbps的传输速度下往低速进行三角展频。这一展频的动作可使信号在传输线及PCB的信号传输时减少电磁干扰问题。

图3:5Gb/ps的传输速度往低速做三角展频。

TX Driver:该模块将5Gbps的高速单端信号转换成高速差分信号,并根据USB3.0规格产生3.5dB/6dB去加重(de-emphasis),在TX端口利用3.5dB/6dB去加重来加强高频的能量,避免传输损失使得眼图的开度变小。

低频周期信号侦测器(LFPS Detector,Low Frequency Period Signal Detector):如果链接处于某种闲置状态,则可通过低频周期信号发送低频周期信号(LFPS)进行通信,这种方式的功耗明显低于SuperSpeed信号发送方式。事实上,不管是主机还是设备发送LFPS,都会退出闲置模式。

RX Receiver:该接收器包含均衡器模块和时钟-数据恢复模块。均衡器接收高速5Gbps的高速信号,并对因传输损失的高频能量做补偿,使时钟-数据恢复模块在锁存数据时,眼图拥有较大开度。

串并联(S2P,Serial to Parallel):将接收下来较高速的串行信号转成高速的并行信号。

USB 3.0控制器硬件电路主要处理USB3.0协议的数据与控制路径。接口部分包括两种接口模块:一种是与USB 3.0物理层进行通信的PIPE接口模块,另一种是与SoC芯片内部AHB总线进行通信的AHB总线接口模块,综合结果显示总线速度可以超过266MHz。USB 3.0设备控制器结构如图4所示。USB3.0链路层模块(U3LKL)实现了USB 3.0规范第7章 “Link Layer Specification”所要求的指标,整个模块始终工作在125MHz。

- 基于S3C44B0X的心电血压监测仪USB接口设计(11-28)

- C8051F320在USB设计中的应用(01-18)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 用CP2101将USB口扩展成串口(01-18)

- TM1300 PCI-XIO口的UART和USB接口设计(01-17)

- 基于CH371的实用USB接口设计(01-23)