用于相变存储器的GeSbTe MOCVD共形淀积

成功地将CVD或ALD淀积的GST合金用于PCM,要求在填充10-100nm高深宽比具有合适材料特性的约束结构中有非常可靠的共形淀积,这些特性包括无空洞淀积、对SiO2和上/下金属电极的粘附性好,以及在400℃时材料性质稳定,能经受随后的器件加工步骤。也需要这样的合金,即能有低复位电流、至少1×106的高循环寿命、10年数据保持温度高于85℃、短置位时间或快速置位、在置位或晶态时阻抗低及复位或非晶态时阻抗高。满足这些要求将提供非晶相和晶相之间一个宽范围电阻率,这是多层单元储存(MLC)应用所希望的。

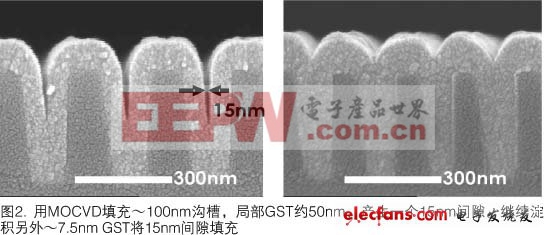

ATMI开发了能填充深宽比大于3:1、尺寸小于15nm结构的MOCVD工艺(金属有机物化学气相淀积),见图2。CVD工艺是优选工艺,因为其产出比ALD工艺快,且有同样大小的批次。ATMI的MOCVD工艺非常有效,因为与典型的CVD工艺比较,它设计使用能在较低温度下加工的金属有机前驱物。ATMI也获得了基础和先进器件应用所需的材料物理性质和优良的电学性质,包括置位速度达12ns的DRAM的可行性。

本文介绍了从开发成熟的MOCVD淀积GST材料性质获得的电学特性。一是用MOCVD淀积的325GST合金,与PVD GST合金比较,它减少复位电流2-3x,显示了NOR闪存应用的可能性。二是用MOCVD淀积的415GST合金,其置位速度65ns,10年数据保持温度118℃,比PVD GST 225合金高出近20℃,有望在SCM中有更高的速度以及在更高的温度环境下应用。

高深宽比结构的GST填充

所做的研究中,高深宽比结构能用多种不同组分的GST适当填充。图1显示了进行的多种组分试验。 获得了GST共形淀积(在GST相图左下的橙色区域),包括成功地填充40nm高深宽比孔洞和用Ge掺杂富Sb的SbTe深宽比为5:1的结构。GST相图右下的绿色区域是Te含量大于50%的富Te GST合金,包括最近得到的325和415合金组分。高性能PCM应用一般需要高Te% GST合金,因为它们结晶温度低。因为一般的淀积薄膜是结晶体,因而不平整也不共形,这是淀积中典型前驱物需用的高淀积温度的结果。图1示出了用ATMI MOCVD工艺在高深宽比通孔中GST325和415填充情况。在我们最近的300mm MOCVD工艺示范中,也成功地达到能以平滑和共形薄膜填充15nm小沟槽结构,Te组分~50%(图2)。

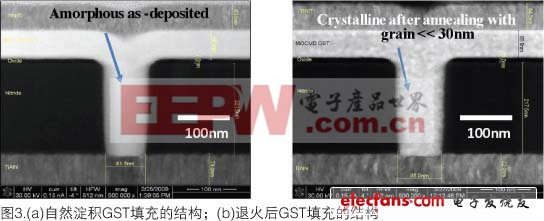

在约束结构中自然淀积的GST可能完全是非晶的,退火后能转变为晶体,分别如图3a和3b所示。请注意,得到了~5nm的极细晶粒。晶粒尺寸非常小对于未来GST向小于10nm结构缩小是很重要的。

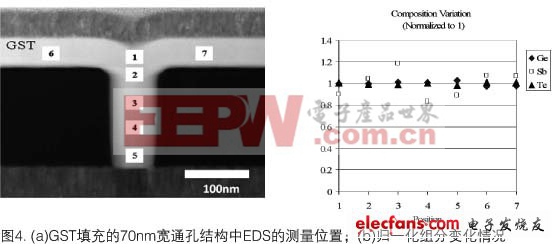

在所做的工作中,GST填充的孔洞内的组分非常一致。图4(a)和4(b)是用EDS测量的归一化组分,通孔中位置1到5(对应通孔结构的顶部到底部)Ge、Sb和Te的分布非常一致。位置6和7(对应通孔的外部二侧)的组分也与位置1-5的类似,说明在薄膜共形淀积过程中得到了极好的组分分布。测得的Sb分布变化较大,可能是由于用EDS测量Sb的不准确性,因信号小而准确性低。

器件性能

复位电流

图5(a)示出了PVD和MOCVD GST合金间器件复位电流性能比较测试结果。图5(b)示出了用N和C掺杂的MOCVD GST325、用N和C掺杂的MOCVD GST225及没有N和C的PVD GST225制作的PCM器件复位-电流(R-I)和I-V曲线的重叠情况。所有这些器件的名义尺寸是100nm,测得的尺寸MOCVD GST325为103nm,MOCVD GST225 和PVD GST225为106nm。在用MOCVD GST325制作的器件中,置位阻抗小于10kΩ而复位阻抗大于1MΩ,表明置位(结晶相)和复位(非晶相)之间有100x以上的动态范围(见图4(b))。用MOCVD GST325制作的器件中的复位电流是0.6mA,比用PVD GST225制作的器件的复位电流1.4mA小2x以上。复位电流减小可使更多器件平行编程,提高了对将PCM延伸

- 基于SPWM控制全数字单相变频器的设计及实现(11-16)

- 铁电存储器及其在电表存储中的应用(06-28)

- flash接口电路的实现(07-18)

- 基于AT89S52汉字多方式显示屏的设计(01-06)

- 3D集成电路将如何同时实现?(04-09)

- 快速创建存储器接口的设计(10-22)