带有增益提高技术的高速CMOS运算放大器设计

时间:11-05

来源:互联网

点击:

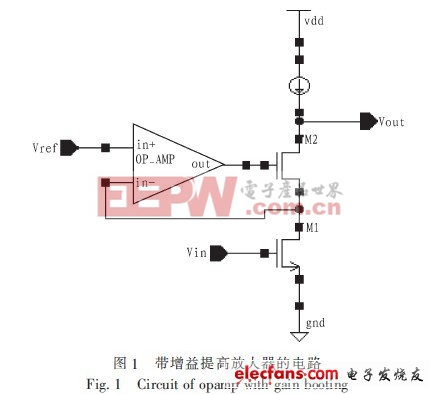

设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14 bit精度,100 MS/s采样频率的高速流水线(Pipelined)ADC的运放。设计基于SMIC 0.25 μm CMOS工艺,在Cadence环境下对电路进行Spectre仿真。仿真结果表明,在2.5 V单电源电压下驱动2 pF负载时,运放的直流增益可达到124 dB,单位增益带宽720 MHz,转换速率高达885 V/μs,达到0.1%的稳定精度的建立时间只需4 ns,共模抑制比153 dB。

- 一种增大放大器增益的方法(11-28)

- 改善可编程增益放大器性能的一个技巧(05-21)

- 运用负反馈模型分析实际运算放大器电路(05-07)

- 在数据转换系统中校准增益误差的方法(03-23)

- 一个对温度不敏感的高增益运算放大器设计(09-16)

- 增益天线种类详解(11-12)