采用综合学科研究法有效封装MEMS加速仪(二)

纹,但是封装不符合共振要求。

表1材料特性和各种固晶的固有频率

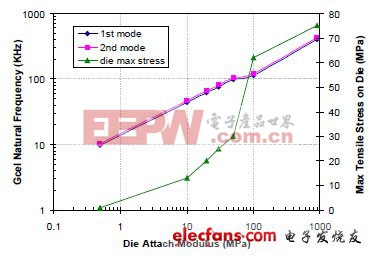

因此进行了一项研究,确定理想的固晶材料的属性的范围,以及对封装共振频率和芯片应力的影响。图5给出了根据固晶模量计算的感应单元的固有频率,以及感应单元基片承受的相应的最大张应力。

图字:gcel natural frequency(kHz):感应单元固有频率(kHz);1st mode:第一模态;2nd mode:第二模态;die max stress:芯片最大应力;Max tensile stress on die(Mpa):芯片承受的最大张应力(Mpa)

图5 根据固晶模量计算得出的感应单元基片的最大张应力和封装共振频率

研究发现,与修改热膨胀系数[4]相比,芯片应力对固晶模量更加敏感。从图5可以看出,模量接近10的固晶材料具有较低的芯片应力,并且满足共振频率要求。

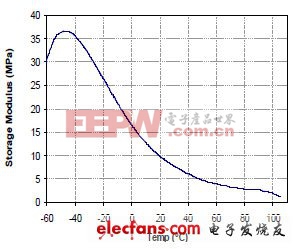

经过一些研究后,我们发现固晶材料E满足我们的性能要求。为了确保采用新固晶胶的芯片的共振性能足够满足要求,我们对材料模量随温度的变化进行了测量。同时进行了动态力学分析(DMA)。对测试样本进行了处理,将材料放到一个扁平的预成型的腔中并进行固化处理。然后测试样本随温度的变化。图6显示了材 料的模量。

图字:storage modulus (MPa):储能模量(MPa);Temp:温度

图6 固晶胶E的存储模量

用内部确定的固晶E的性能对封装进行的模态分析表明,它的固有频率大于20 kHz。此外,图4显示了固晶E的裂纹扩展能量与固晶A相似,因此不会产生芯片断裂的问题。因此,固晶胶E被用于替换固晶胶D,因为它非常柔韧,不会使芯片断裂,同时也具有足够的硬度,满足共振要求。对这种新的固晶材料进行鉴定检测和试封装后发现,整个测试样本中没有出现任何芯片断裂。

结语

本文16引线SOIC加速仪封装的完整工艺流程进行了评估解以了解造成低ppm水平芯片断裂的裂纹扩展和倾向。找出了两个危害最大的关键工序。影响最大的是焊接回流工序,其次是引线粘结工序。引起芯片断裂的主要参数是感应单元固晶胶的硬度。目前使用的固晶胶D使感应单元基片芯片非常容易出现断裂。通过反向工程确定了可以同时满足感应单元固有频率和封装可靠性需求的固晶材料。采用推荐的固晶胶E后,封装在处理通常会引入裂纹和感应单元固有频率要求的工艺时表现更加强韧。

- 基于MEMS的硅微压阻式加速度传感器的设计(11-03)

- 压电振动式发电机微电源智能控制应用电路的设计(01-09)

- 低压驱动RF MEMS开关设计与模拟 (10-01)

- MEMS时钟让手机设计占位更小功耗更低(04-07)

- SiTime:延长电池寿命,从大局考虑(07-18)

- 降低封装测试成本,MEMS产品封装设计要点(01-31)