采用线阵CCD的便携式光谱采集系统设计(一)

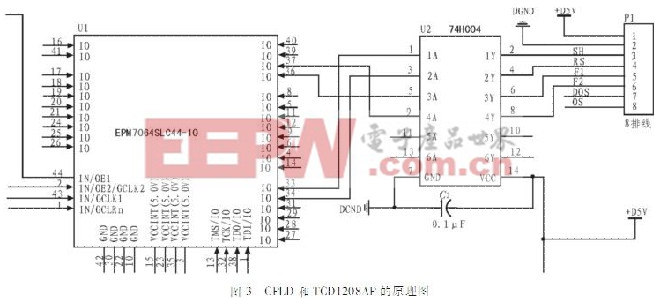

作为本文的光电转换器件,其需要四路时钟脉冲的驱动:SH,φ1,φ2,RS。四路脉冲的幅值为5 V,属于标准的TTL逻辑电平。在驱动设计时可以使用微处理器来实现也可以使用FPGA或者CPLD等逻辑阵列来实现。但微处理器的时钟精确度相对于逻辑阵列比较低,且存在相位不同步的问题,因此,本文设计的方案使用CPLD来实现,其芯片为Altera公司的MAX7000系列的EPM7064SIA4,其IO口具有5 V电平的输出能力,可以和TCD1208AP直接连接而无需其他电平转换芯片,硬件连接图如图3所示。

CPLD使用10 MHz的有源晶振输入,为了提高CPLD的驱动能力,使用了反相器74HC04对CPLD输出的驱动脉冲进行放大,由于74HC04的反相作用,因此,CPLD的驱动脉冲的高低电平与正常驱动CCD的脉冲必须是反相的。CPLD输入的时钟clk为10 MHz,通过HLD硬件编程语言实现十分频,输出1 MHz的CCD复位脉冲。

1.2 节讨论利用VOS与VDOS的加减运算来实现光谱

信号中直流电平的滤除,硬件则利用运算放大器来实现这一过程。本系统采用AD公司的AD8051运算放大器,其工作带宽最高达110MHz,较低的建立时间使得其处理高频信号的能力较强,根据基本运算放大器计算规则,得出输出信号Vout为:

调节R9的值则可以改变Vout的输出值,此时的Vout就是没有直流电平的物质光谱吸收信号。

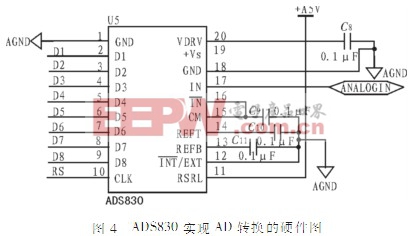

经过处理后的物质吸收光谱信号,进入AD转换模块,在该模块可以对光谱信号中的复位脉冲进行滤除,从而得到有效的光谱信号。采用的AD转换芯片是BB公司的8 bit模拟到数字转换芯片,其采样率可以达到60 MHz以及49.5 DB的高信噪比,使得其转换速率和精度满足光谱采集系统的高速和高精度的要求。ADS830需要4个时钟周期才能完成数据采样和数字信号的输出,在接收ADS830转换的数字信号时需要控制好接收数据的时刻,以便准确无误的得到需要的数据。

图4为使用ADS830来进行光谱数据数字化的转换电路,ANALOGIN输入则是通过AD8051后处理的不带直流电平的光谱数据。由于ADS830的输入端电压范围是1.5~3.5 V,因此,为了使得经过AD8051的光谱信号处于这一范围,需要通过调节R9的值来实现。D1~D8则是转换后的光谱信号,该信号送入微处理器进行后续处理。

- 用于下一代移动电话的电源管理划分(08-28)

- CCD信号采集系统的USB接口设计(03-12)

- 基于CPLD的线阵CCD驱动电路设计(01-24)

- CCD时代将被CMOS终结?(05-17)

- 基于高速多通道CCD预放电路的设计方案(10-25)

- 基于KAI-01050 CCD功率电路的驱动方案(06-10)