FPGA+DSP的高速通信接口设计与实现

,LxCLKIN信号仍然为高,则肩动数据传输(以上时钟信号都以发送端视角分析)。本设计中,令牌转换模块负责验证令牌和发送令牌。这里要注意,由于用来验证令牌低电平个数的时钟信号(PLL_32ns)是由FPGA时钟信号(CLK)通过锁相环倍频得到,与DSP链路口时钟异步,故验证令牌时,当计数器计到5个低电平时即可认为已达成通信握手,否则可能会丢失数据。达成握手后通知控制模块向接收或发送缓存输出控制信号,其中接收控制信号包括写缓存时钟和写使能。发送控制信号包括读缓存时钟、读使能和DSP中断信号(DSP_IRQ),其中写缓存时钟通过对链路口时钟分频得到,读缓存时钟由锁相环倍频FPGA工作时钟得到。

(3) 发送部分:与接收部分类似,也南编码和缓存两部分组成,相应的设计基本相同,这里不作过多介绍。由于DSP链路口每次传输数据个数的最小单位是4个32位字,即8个链路时钟周期,所以发送时钟廊该每8个时钟周期一组,以凑够128bit,避免传输错误,其中多余无效的数据DSP可以自行舍去。发送部分采用DSP外部中断方式而不是链路口中断方式通知DSP接收数据。

TS101的链路口通信协议要求链路口接收端在传输启动一个周期后,将其LxCLKOUT拉低,若可以继续接收,在下一个周期再将其拉高,以此作为连接测试。实际运行中发现,当FPGA接收数据时,可将LxCLKOUT信号一直驱动为高,不必做特殊的连接测试也能正确接收数据。另外,发送链路口数据时,由于发送缓存中已经对应仔好了要发送的8bit数据,故可以使用对FPGA时钟信号(CLK)倍频得到的PLL_16ns信号来读发送缓存,读出的数据即链路口发送数据,再对PLL_16ns信号的下降沿分频得到链路口的发送时钟信号。

限于篇幅,本文只给出FPCA接收TS101数据的时序图,如图3所示。LxCLKIN、LxDAT[7..0]是DSP的链路口输出时钟和数据,LxCLKOUT是FPGA的回馈准备好信号。仿真中链路口数据采用1F-3E(十六进制)的32个8bit数据,即从2221201F到3E3D3C3B的8个32bit数据;PLL_32ns信号是FPGA内部锁相环产生的与DSP链路口时钟异步的32ns时钟信号,用来校验令牌指令;W_FIFO_EN信号足写缓存使能信号,当令牌验证后使能接收缓存;DSP_DAT信号是DSP通过链路门传输的32bit数据,通过对链路口数据的编码得到;W_BUF_CLK信号由链路口时钟分频处理得到,将上升沿对应的32bit DSP数据写入接收缓存,完成接收过程。

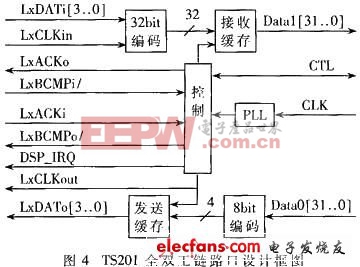

2.3 基于FPGA的TS201链路口设计

图4给出了FPGA与TS201进行链路口通信的设计框图。由于TS201的握手信号较多,所以相对TS101的链路口设计容易些。本设计FPGA时钟50MHz,TS101核时钟500MHz,链路口时钟为DSP核时钟的4分频,采用4bit方式,单向实际数据传输速率为125MBps。

TS201的链路口数据和时钟采LVDS信号,具有速率高、功耗低、噪声小的优点。Cyclone系列芯片不仅支持LVDS信号,还集成了LVDS转换模块,这给设计提供了很大方便。应该注意的是,在硬件设计时LVDS信号两极的PCB走线要匹配,并且注意匹配电阻网络的接入。

TS201的链路口有1bit和4bit两种传输方式,本文以4b it为例进行设计。图4给出的信号都是经LVDS转换后的信号。由于TS201的收发做成了两个单独的通道,FPGA的设计也应该相应地设计为两个通道,真正做到全双工通信,收发互不影响。接收与发送部分与TS101的设计基本相同,发送部分也采用外部中断方式通知DSP接收链路口数据。TS201的通信握手信号有ACK和BCMP#信号。其中ACK信号用来通知接收准备好,在实时信号处理中,一般不允许数据传输的等待,故将这个信号置为准备好。BCMP#信号用于通知数据块传输的结束,当能确定DMA传输数据个数时,可以将此引脚悬空。

TS201链路口的收发机制非常相似,本文仅给出发送数据时序图,如图5所示。L1_IRQ是FPGA发给DSP的外部中断,用来通知DSP收数据;L1_ACKI是DSP的接收准备好信号;R_BUF_EN是读发送缓存使能信号;链路口时钟L1_CLKOUT是以读缓存时钟R_CLK下降沿的二次分频,对应从缓存中读出的4bit链路口数据L1_DA-To。注意这里读缓存及时钟分频时会有纳秒级的延迟。

3 DSP的相应设置

TS101和TS201的链路口都配置了控制寄存器(LCTLX)和状态奇存器(LSTATx)两组寄存器。LCTLx用来控制链路口的传输,LSTATx用来通知链路口的工作状态。TS101链路口时钟频率可以是核时钟的8、4、3或2分频,通过设置LCTLx中的SPD位米完成,本文设计将SPD位置000,即为核时钟8分频。由于TS201的接收发送通道独立,所以其控制寄存器分为接收控制寄存器(LRCTLx)和发送控制寄存器(LTCTLx)。TS101链路口发送时钟频率可以与核时钟

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)