ADI实验室电路:完整的HART兼容型4mA至20mA解决方案(一)

过高可能会干扰设备本身或网络上其它设备对HART信号的接收。

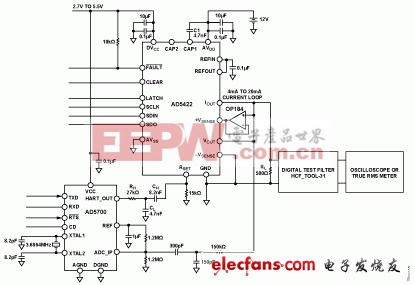

对于在500Ω负载上测得的电压噪声,其包含的扩展频带中的宽带噪声和相关噪声总和不能超过2.2 mV rms。此噪声通过在500Ω负载上连接HCF_TOOL-31滤波器(可从HART通信基金会获得)并将滤波器输出连接到真均方根测量仪(参见图6)来测量。也可使用示波器来检查输出波形峰峰值电压。

AD5422 输出电流设置为4 mA、12 mA和20mA。对于所有这三个输出电流值,有带通滤波器时的结果十分相似,不过电流输出值增加时,宽带宽噪声也略有增加。在输出电流为4 mA的情况下,使用和不使用HCF_TOOL-31带通滤波器时,测得的均方根值分别为143μV rms和1.4μV rms。这两个值均在要求的2.2 mV rms(使用HART滤波器)和138 mVrms(不使用HART滤波器的宽带噪声)规范内。在输出电流为12 mA的情况下,使用和不使用HCF_TOOL-31带通滤波器时,测得的均方根值分别为158μV rms和2.1μV rms,这两个值同样都在HART协议规范要求的范围内。

图6. HART规范测试电路

图7和图8分别显示4 mA和12 mA输出电流的示波器曲线图。注意,滤波器的通带增益为10。每个曲线图上的通道1和通道2分别显示滤波器的输入和输出。

图7. 输出电流为4 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

图8. 输出电流为12 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

模拟变化率

此规范可确保当设备调节电流时,模拟电流的最大变化率不会干扰HART通信。电流的阶跃变化会扰乱HART信号。仍然使用如图6所示的相同测试电路。为进行这个测试,AD5422被编程为输出一个4 mA至20 mA切换的周期波形,该波形在两个值上都没有延迟,以获得最大变化率。为了符合HART规范,滤波器输出端波形的峰值电压不能大于150 mV。符合这一要求可确保模拟信号的最大带宽处于规定的直流至25 Hz频带中。

AD5422输出从4 mA变为20 mA的正常时间约为10μs。这个速度显然太快,而且会对HART网络造成重大破坏。为了降低变化率,AD5422提供了两种特性:一是在CAP1和CAP2引脚处连接电容,二是提供内部线性数字压摆率控制功能(详情请参考AD5422数据手册)。对于较快的压摆率,可在与AD5422通信的控制器/FPGA上实施一个非线性数字斜坡发生器。

要使带宽降低到25 Hz以下,需要在CAP1和CAP2引脚处连接非常大的电容值。最佳解决方案是结合使用外部电容和AD5422的数字压摆率控制功能。两个电容C1和C2的作用是降低模拟信号的变化率;不过还不足以满足规范。使能压摆率控制功能可以为变化率的设置提供灵活性。

图9. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 3,SR阶跃= 2,C1 = 4.7 nF,C2 = NC

图9显示了AD5422的输出和HART滤波器的输出。滤波器输出端的峰值电压为82 mV,处于规定范围以内。压摆率设置为SR时钟= 3和SR阶跃= 2,从4 mA至20 mA的转换时间设为约120 ms,C1 = 4.7 nF,C2未连接。如果这个变化率太低,可以缩短压摆时间。采用C1 = 4.7 nF且C2未连接的电路配置时,可以发现压摆时间设为80 ms(SR时钟= 1,SR阶跃= 2)时,所得到的模拟变化率符合HART规范。然而,如果将压摆时间进一步缩短至60 ms(SR时钟= 0,SR阶跃=2),则会导致结果超出150 mV规格范围。从CAP1接至AVDD的电容可用于抵消滤波器输出端因压摆时间过快而导致的峰值电压增加。然而,选择此值时必须小心,因为它会影响“确定外部元件值”部分讨论的低通滤波器截止频率。

图10显示了压摆率控制设置改为SR时钟= 5、SR阶跃= 2且C1电容值保持4.7 nF不变的结果。这样,转换时间就会在240 ms左右。滤波器输出端的峰值幅度可通过增加C1值、配置更慢的压摆率或通过两者的组合来进一步降低。

图10. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 5,SR阶跃= 2,C1 = 4.7 nF,C2 = NC

- ADI实验室电路:集成冷结补偿的K型热电偶测量系统(10-16)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)