运放电源去耦旁路措施

时间:10-23

来源:互联网

点击:

本文介绍了运放电源的去耦旁路电容的接法。

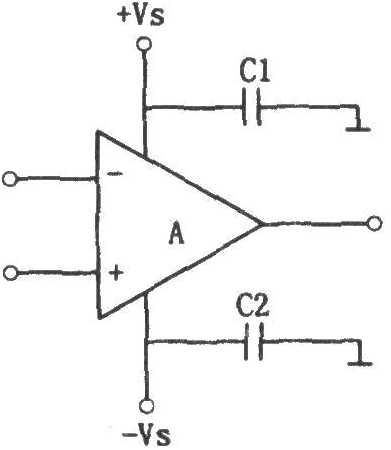

每个集成运放的电源引线,一般都应采用去耦旁路措施,即从电源引线端到地跨接一个高性能的电容,如图所示。图中的高频旁路电容,通常可选用高频性能优良的陶瓷电容,其值约为0.1μF。或采用lμF的钽电容。这些电容的内电感值都较小。在运放的高速应用时,旁路电容C1和C2应接到集成运放的电源引脚上,引线尽量短,这样可以形成低电感接地回路。当所使用的放大器的增益带宽乘积大于10MHz时,应采用更严格的高频旁路措施,此时应选用射频旁路电容,如0.1μF圆片陶瓷电容,同时每个印刷板或每4~5个集成芯片再增加一对(C1和C2)钽电容。对于通用集成芯片,对旁路的要求不高,但也不能忽视,通常最好每4~5个器件加一套旁路电容。不论所用集成电路器件有多少,每个印刷板都要至少加一套旁路电容。

电路具体处理

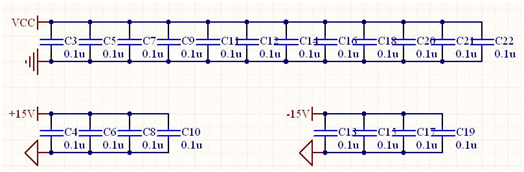

我们可以在电路中数数有多少个芯片有几个电源端(正负电源),在每个电源端都接一个去耦电容到地端。有时在电路图上可以看到下图所示的这样,电源连了很多电容到地端,其实这些就是去耦电容,在布PCB时,要在芯片电源端就近布置这些去耦电容,而不应该把去耦电容在电源部分都布了,这样的话就起不到去耦的作用。

- 单运放构成的单稳延时电路(11-29)

- 运放电路设计中无源元件的选择(01-23)

- 高速应用中电流反馈运放电路设计分析(01-06)

- 基于GB3442-82的集成运放参数测试仪设计 (03-05)

- D类音频系统中斩波运放电路的设计(03-25)

- 被完全误解的三运放仪表放大器(05-24)