高速转换器简介和工作原理

10 MHz或以上的带宽。

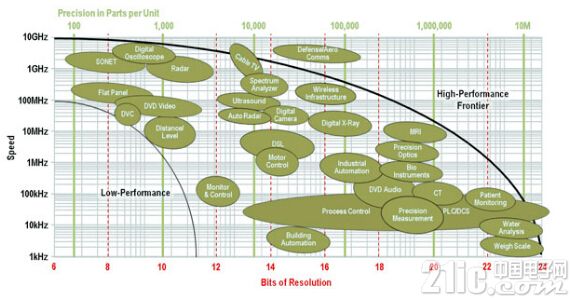

3.所示为一些典型应用对带宽(速度)和动态范围(分辨率位数)的要求。

需要注意的是,该“应用图”并非静止不变——现有应用可能利用新的、性能更高的技术来提升其功能,例如,高清摄像机或者分辨率更高的“3D”超声设备等。 每年还会涌现出全新的应用,很大一部分处于性能边界的“外边缘处”,这得益于高速与高分辨率的新组合。 结果使转换器性能“边缘不断扩大”,就像池塘里的涟漪一样。

另一个重点是大多数应用具有功耗问题。 对于便携式/电池供电型应用,功耗可能是主要技术限制条件,但是,即使是线路供电系统,我们也开始发现,信号处理元件(模拟也好,数字也好)的功耗最终会限制系统在给定物理区域的性能。

技术发展趋势和创新——如何实现

鉴于这些应用在不断推高对高速数据转换器性能的要求,业界以持续技术进步的方式对此做出了回应。 技术对高级高速数据转换器的“推动”来自以下几个因素:

• 工艺技术: 摩尔定律与数据转换器——半导体工业在持续推动数字处理性能方面的成就有目共睹,其主要驱动因素是晶圆处理工艺在走向更细间距微影蚀刻工艺方面取得的巨大进步。 深亚微米CMOS晶体管的开关速率远远超过其前辈,使控制器、数字处理器和FPGA的运行时钟速率迈上了数GHz的台阶。

像数据转换器一样的混合信号电路也可以利用蚀刻工艺领域取得的这些进步,借“摩尔定律”之风达到更高的速率。 但对混合信号电路来说,这是有代价的:蚀刻工艺越先进,其工作电源电压往往会越低。 这导致模拟电路的信号摆幅在缩小,增加了将模拟信号维持在热噪底以上的困难——以缩水的动态范围为代价获得更高的速率。

• 高级架构(这不是祖母时代的数据转换器): 在半导体工艺大步发展的同时,过去20年中,高速数据转换器架构领域也出现了数波创新浪潮,为以惊人的功效实现更高的带宽、更大的动态范围做出了巨大贡献。 传统上,有多种架构方式用于高速ADC,包括全并行架构、折叠架构、交织架构和流水线架构,这些架构方式至今仍然非常流行。 后来,传统上用于低速应用的架构也加入高速应用阵营,包括逐次逼近寄存器(SAR)和Δ-Σ,这些架构专门针对高速应用进行了的改动。

每种架构都有自己的优势和劣势。 某些应用一般根据这些折衷来确定“最佳”架构。 对于高速模数转换器(DAC)来说,首选架构一般是开关电流模式结构。 不过,这类结构有许多变体。 开关电容结构的速率稳步提高,在一些嵌入式高速应用中仍然十分流行。

•“数字辅助”方法: 多年以来,在工艺和架构以外,高速数据转换器电路技术也取得了辉煌的创新成就。 校准方法已有数十年的历史,在补偿集成电路元件失配以及提高电路动态范围方面发挥着至关重要的作用。 校准已经超越静态误差校正的范畴,越来越多地用于补偿动态非线性度,包括建立误差和谐波失真。

总之,这些领域的创新极大地促进了高速数据转换的发展。

实现

实现宽带混合信号系统不仅仅要选择正确的数据转换器——这些系统可能对信号链的其他部分有着严苛的要求。 同样,挑战是在较宽的带宽范围内实现优秀的动态范围——使更多的信号进出数字域,充分利用数字域的处理能力。

• 宽带信号调理: 在传统“单载波”系统中,信号调理就是尽快消除无用信号,然后放大目标信号。 这往往涉及选择性滤波以及针对目标信号“微调”的窄带系统。 这些经过微调的电路在实现增益方面可能非常有效,而且在某些情况下,频率规划技术有助于确保将谐波或其他杂散排除在“带外”。 宽带系统不能使用这些窄带技术,而且在这些系统中实现宽带放大可能面临巨大的挑战。

• 数据接口: 传统的CMOS接口不支持大大超过100 MHz的数据速率——而且低电压差分摆幅(LVDS)数据接口运行速率达800 MHz至1 GHz。 对于较大数据速率,我们可以使用多个总线接口,或者使用SERDES接口。 现代的数据转换器采用的是最高速率达12.5 GSPS的SERDES接口(规格见JESD204B标准)——可以用多条数据通道来支持转换器接口中分辨率和速率的不同组合。 这些接口本身常常十分复杂。

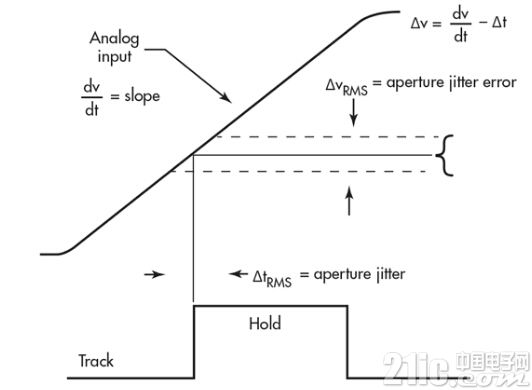

4.时钟抖动/误差变成信号噪声或误差。

• 时钟接口: 就系统中所用时钟的质量来说,高速信号的处理也可能十分困难。 时域中的抖动/误差会转换成信号中的“噪声”或误差,如图4中的信

- 新型人机对话接口与音频数据转换器技术及选用(05-23)

- 混合信号系统接地揭秘(07-22)

- 初步了解信号链中的数据转换器(11-17)

- 合适数据转换器选择:JESD204B与LVDS技术对比(09-15)

- Delta-sigma数据转换器的抗混滤波器设计方案(08-06)

- TI:电源创新中的热门趋势(04-15)