基于AD9680的宽带高动态全数字雷达接收机设计

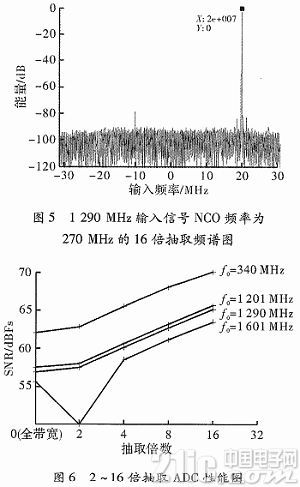

系统采用内置4个数字下变频器DDC0-DDC3的 AD9680对回波进行采集和处理。本文对AD9680在DDC模式下的性能进行验证、分析和改善,具体过程如下:外部时钟输入后,通过设置DDC抽取倍数、NCO相位值、JESD204B关键性能参数等得到输入信号的FPGA数据输出,计算输出数据的ADC性能值并对其进行分析和改善。部分频点抽取后频谱及性能如图5和图6所示。

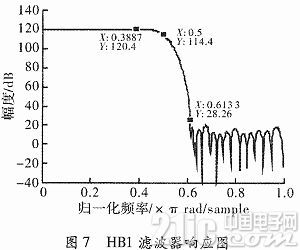

随着抽取倍数的提高,系统的重构速度变快。在经过AD9680内置的DDC模块后,频段为1.2~1.4CHz的信号其满量程FPGA数据输出SNR(Signal Noise Ratio)值可达63 dBFs,ENOB可达10位,可保证前端输入噪声加信号能够被ADC充分量化。验证过程发现系统存在以下两个问题:在过采样和滤波条件下,DDC理想SNR改善为

,即2倍抽取时理想SNR和全带宽模式相近,在2倍抽取的基础上抽取倍数每提高一倍,相应复数输出数据或上变频后实数输出数据的理想SNR性能值提高3 dB,而图6中SNR性能值实际只提高了约2.5 dB;部分频点2倍抽取时性能明显偏低,如图6中的1 601 MHz输入信号。分析可知,影响问题1的主要因素是滤波器的性能,影响问题2的主要因素是在2倍抽取的有效带宽范围内混入了杂波。

(1)系统在进行2n倍抽取时信号先后经过滤波器HB(n),HB(n-1)…HB1,n=4,3,2,1,由此,HB1是滤波器的最后一级。本文以 HB1滤波器为例,分析随着抽取倍数的变大,实际SNR性能值应提高的幅度。系统采用的HB1滤波器有55个抽头系数,其滤波器响应如图7所示。

2n倍抽取后信号带宽为fs/2n,图中滤波器在抗混叠抑制要求>85 dB时,保护带宽为fs/2n×38.9%,即(fs/2n×50%,fs/2n×61.1%)的噪声分量在一定程度上会混入 (fs/2n×38.9%,fs/2n×50%)。由图7可看出,滤波器在(fs/2n×50%,fs/2n×61.1%)这段频率范围的响应近似为一条斜线,即近似滤除该频段一半的噪声分量。故2n倍抽取时HB1滤波器在前一级滤波器的基础上对性噪比的实际改善为

,即2.55 dB。实际中噪声分量不是绝对均匀的,某些点频信号的噪声分量可能存在偏大或偏小的情况,但实测结果与本文计算的实际SNR性能改善值差别较小。

(2)由前面的分析知DDC2倍抽取的SNR性能值应稍大于全带宽模式,而图6中当输入信号为1601MHz时,2倍抽取的ADC性能值明显偏低。为此,对系统输入信号的DDC 2倍抽取进行Matlab仿真,发现2倍抽取性能变差的主要原因是镜像分量的混入:采集信号先后经过频率为fNCO的数控振荡器和半带抽取滤波器做数据输出。当信号与其的镜像分量与NCO进行运算后同时出现在滤波器HB1的通带内或镜像分量在HB1的过度带内时,滤波器无法将其滤除干净,镜像分量混入2倍抽取后信号的有效带宽内,导致输出数据的ADC性能变差。为了实现某雷达频段的射频信号直接采样,必须采用带通采样或欠采样,因此需采用模拟抗混叠滤波器来抑制其他奈奎斯特频带的干扰或噪声,防止干扰混叠或噪声折叠对输出信噪比的影响。

2.3 系统同步性验证

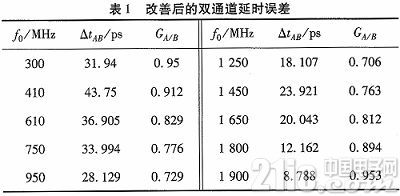

宽带雷达数字接收机多个通道之间的相位差大小决定后期成像质量的优劣。本系统用功分器将信号源输入在2 GHz以下的信号分成两路输送给ADS7-V1EBZ的通道A和通道B,对输入信号进行全带宽和数字下变频模式数据采集,采用正弦信号在时域上的自相关和互相关计算两个通道输出数据间的增益误差和时间偏差。分析知延时误差由以下几个因素导致:(1)两个输入信号在电路板上的布线差异。(2)AD9680芯片内部两个通道问的差异。(3)信号经过功分器和接线后产生时间误差。以上使两个通道输出数据相位和频率不完全同步的因素可通过下列方法进行改善:1)优化电路设计。2)调节NCO相位值。3)算出功分器和接线的延迟误差并将其去除。本文去除了由功分器和接线造成的延迟误差并对系统下变频的NCO相位值进行了调整,优化后的双通道延迟误差如表1所示。

其中,f0为输入信号频率;△tAB和GA/B分别为两个通道之间的时间偏差和增益误差。为减小对后期成像的影响,需消除雷达系统的通道相位失真,即在实现双通道回波的高速采集和处理的同时需要达到一定的相位一致条件。本设计的通道A和B分别对应某雷达的水平和垂直两个极化通道,改善后的双通道延时误差在 45 ps以下,满足接收机的应用需求。

3 结束语

本文通过分析基于AD9680的宽带雷达数字接收机验证平台的基本特点及两种工作方式,结合雷达系统的实际要求,对系统FPGA输出数据进行性能验证、分析、验证和改进。并对ADS7-V1EBZ两个信号输入通道间的同步做了验证与分析,提出了双通道延时误差的改善方案。结果表明,新型

AD9680 宽带雷达数字接收机 JESD204B 数字下变频 双通道同步 相关文章:

- 使用JESD204B同步多个ADC(04-29)

- 合适数据转换器选择:JESD204B与LVDS技术对比(09-15)

- 教你怎么消除影响JESD204B链路传输的因素(09-09)

- IDT打造首款具备JESD204B接口的全新四通道DAC(10-16)

- 基于FPGA的高速数字下变频系统设计(10-16)

- 12位串行A/D转换器MAX187的应用(10-06)