基于多核DSP处理器DM8168的视频处理方法

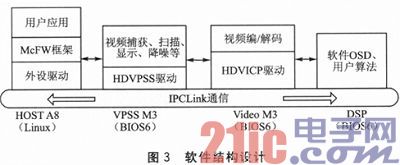

控模块,运行Linux系统,主要负责整个系统的控制以及外设管理;另外3个内核运行BIOS6系统,其中VPSS M3运行在HDVPSS上,主要管理视频的采集、存储以及输入/输出;Video M3运行在HDVICP上,主要负责视频的编解码;C674x DSP主要执行软件的显示策略以及用户算法。软件结构设计如图3所示。

多通道视频处理框架(Multi—channel FrameWork,McFw)中对视频处理常用的捕获、压缩编码、解码、显示等处理过程进行了优化,该框架下的视频处理以Link为基本处理单位进行。视频传递采集、编码以及显示过程大致分为以下几个过程。

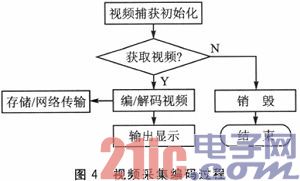

(1)原始采集过程

系统获得采集任务之后,首先初始化采集参数,包括采集设备的检测、需采集的视频格式、输出格式等。稍后调用McFW框架下的System _linkCreate()创建CaptureLink,调用System_linkStart()进行视频采集,模拟信号经过主板上集成的4片TV5158解码芯片之后转换为16ChD1 YUV422i 60fps的数字信号传递给VPSS协处理器,等待下一步处理。

(2)视频处理

VPSS协处理器检测到视频输入以后,对输入的视频进行降噪、去隔行处理等,然后将数据传递给HDVICP协处理器,DM8168内部集成的3个HDVICP协处理器的视频编解码硬件加速支持MPEG4 H.264等视频的编解码格式,运行在HDVICP上的视频编码子系统(Video Encode Subsyst em,VENC)以及视频解码子系统(Video Decode Subsystem,VDEC)具体实现16 Ch D1 60 fps的H.264编码压缩/解码处理。

(3)视频的存储、显示以及传输

HDVICP协处理器压缩产生的视频数据,放入内存共享区,供ARM处理器进行后期的网络传输或本地存储。同时,也将数据传递给HDVPSS协处理器实现16 Ch视频的显示输出。

(4)视频采集的销毁

视频采集结束后,HDVPSS首先调用System_link Stop()停止视频采集,然后调用System_linkDelete()释放占用资源。视频采集编码过程如图4所示。

视频的采集、降噪、压缩编码/解码、显示都由Host A8进行控制,每个视频采集过程中的功能都在各自处理上进行了模块的划分,以独立的线程运行。各模块间通过消息中断、IPC等方式进行通信,通过共享内存实现数据共享。

3 结果测试与分析

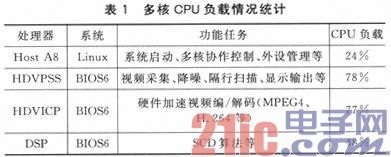

本研究方法中,模拟视频信号经过主板上集成的4片TVP5158解码芯片转换为16Ch D1 YUV422i 60fps数字信号传递给HDVPSS协处理器进行降噪、隔行扫描处理,数据预处理之后HDVPSS将数据传送给HDVICP协处理器进行视频的H.264压缩存储,同时数据也由HDVPSS协处理器的HDMI数据输出接口输出到显示器。多核CPU负载情况统计如表1所列。

实验结果中,Host A8作为主控处理器,负责多核DSP的任务调度和协调,HDVPSS以及HDVICP协处理器承担了16 D1视频的采集以及压缩编码工作,处理器负载较均衡。由于协处理器独立承担视频的处理任务,DSP在本设计中只负责SCD算法,负载较小。整体上来看,由于多核DSP DM8168的各个核心处理器之间相互协同工作,整个系统的负载较均衡,整个系统得到了有效的利用,且性能也比较突出。

结语

针对16通道D1数据格式的大数据量视频数据置的采集编码,在传统达芬奇DSP处理器上实现相对较为困难,而本文针对基于多核DSP DM8 168将视频的采集、降噪、隔行扫描以及压缩编码等任务从传统的单核DSP处理器上独立出来,分别由从硬件加速的HDVPSS协处理器和HDVICP协处理器来完成,极大地提升了视频采集的效率,同时也减轻了单核DSP的任务负担,功能模块化设计大大提升了嵌入式设备的整体处理能力,效果较为明显。但从实际应用的角度来考虑,本设计可能考虑得不够全面,需在后期设计中不断地充实和完善。

- Dialog DA9053为i.MX 6多核处理器提供电源解决方案(08-27)

- 移动设备需要多核处理器吗?(07-04)

- 意法爱立信移动平台多核处理技术(二)(10-14)

- 多核系统中NoC通讯架构的关键技术(二)(10-15)

- 意法爱立信移动平台多核处理技术(一)(10-14)

- 意法爱立信移动平台多核处理技术(三)(10-14)